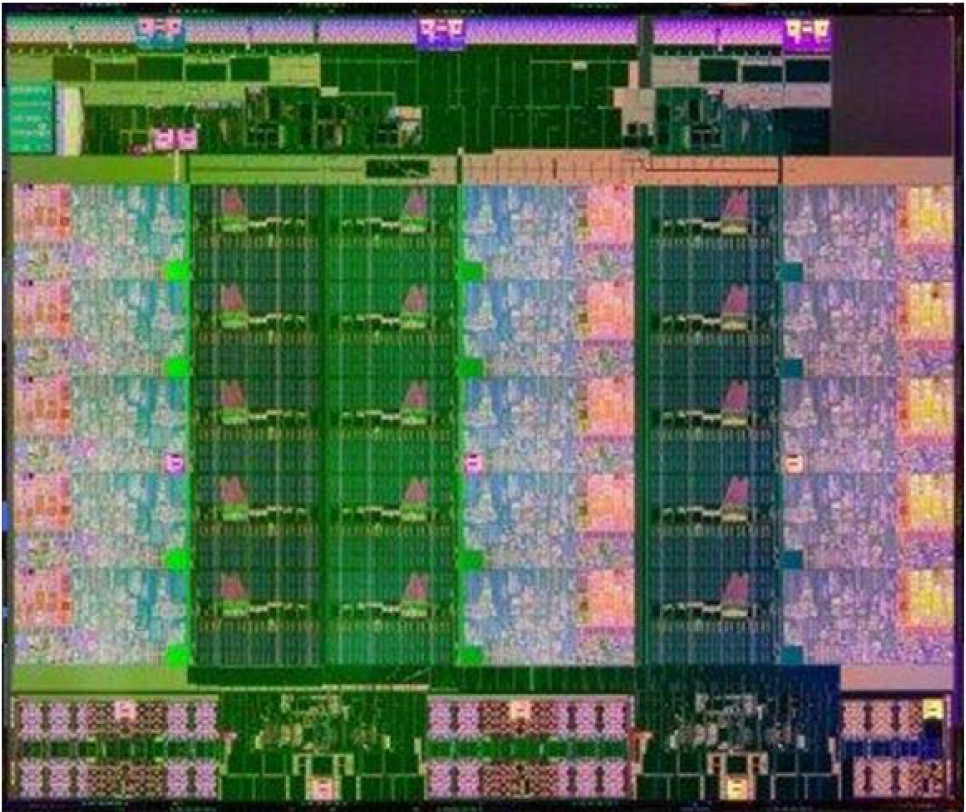

At the International Solid-State Circuits Conference (ISSCC) conference this week, Intel Corp. revealed the first details about its next-generation processor for enterprise-servers code-named Ivytown. The new chip will pack 15 cores and will feature an all-new floor plan and internal interconnections.

The next generation enterprise Xeon server processor has 15 dual-threaded 64-bit Ivy-Bridge cores and 37.5MB shared L3 cache. The system interface includes two on-chip DDR3 memory controllers each with two memory channels (that support 800MT/s – 1867MT/s effective frequencies for traditional DDR3 modules as well as up to 2667MT/s speeds to connect to a memory extension buffer using voltage-mode single-ended (VMSE) interface) and supports multiple system topologies. The Ivytown processor’s high-speed serial I/O’s consist of 40 lanes of PCI Express (2.5/5.0/8.0Gbps), four lanes of direct media interface (DMI) (2.5/5.0Gbps), and 60 lanes of QPI (6.4/7.2/8.0Gbps) interface to connect with other central processing units (CPUs).

The processor consists of 4.31 billion transistors and is manufactured using 22nm process technology. The design supports a wide array of product offerings with thermal design power ranging from 40 to 150W and frequencies ranging from 1.4 to 3.8GHz.

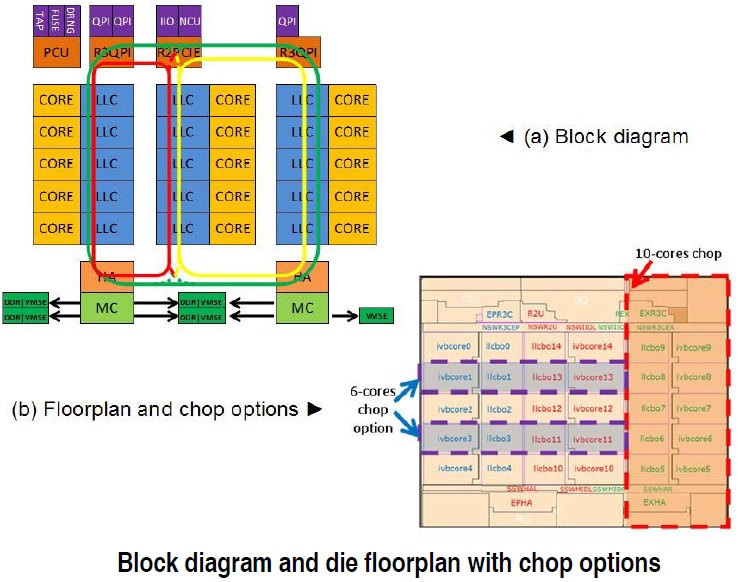

The floorplan of the Ivytown chip is significantly different compared to today’s multi-core chips and is driven by the ring bus routability and latency, as well as the chop requirements to different core counts. The cores and associated L3 cache are organized in columns of five with the ring bus segment embedded. The fully populated die has 15-cores in three columns, but the die can be easily re-configured to create central processing units with lower core counts. For example, the 10-core chop removes the rightmost 3rd column and its dedicated top and bottom I/Os. Since CMOS muxes embedded in the ring bus are programmed to operate in a 2 or 3 columns configuration respectively. The 6-core chop removes the 2nd and 4th rows from the 10-core die.

Intel’s latest processors – Xeon E5 v2 “Ivy Bridge-EP” – have up to 12 cores. Therefore, to fit 15 cores into 140W thermal design envelope, the company had to implement various measures to cut overall power consumption of the chip and reduce power leakage. The “Ivytown” design uses lower-leakage transistors in non-timing-critical paths, achieving 63% usage in the cores and over 90% in the non-core area. Overall, leakage accounts for about 22% of the total power at the typical process corner, quite impressive for a multi-core chip with relatively high frequency.

The “Ivytown” processor is compatible with LGA2011 form-factors, so it can potentially fit into current Xeon E5-supporting servers. Intel has not announced when and whether the Ivytown will be released, but if it makes it to the market, this will likely happen this year.

KitGuru Says: 15 dual-threaded Ivy Bridge cores will offer unbeatable alternative to AMD’s 16-core Opterons currently available on the market. Looks like Intel’s dominance on the server market is going to get even stronger this year.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

One comment

Pingback: Intel Details 15-Core Xeon E7 Ivytown and Haswell Microarchitecture Details at ISSCC 2014