At the International Solid-State Circuits Conference 2015 Advanced Micro Devices unveiled the first official details regarding its code-named “Carrizo” accelerated processing units. As reported, the new chips are aimed specifically at notebooks and therefore were designed from the ground up to be extremely power efficient and integrate all functionality possible.

AMD “Carrizo” accelerated processing units feature four x86 cores based on the “Excavator” micro-architecture, the pinnacle of “Bulldozer” family evolution, Radeon R7 graphics processing unit with 512 stream processors featuring GCN 1.2 architecture, advanced multimedia engine with hardware 4K/UHD video decoding, a dual-channel DDR3 memory controller as well as an built-in I/O controller. The “Carrizo” is the first APU to comply with heterogeneous system architecture (HSA) 1.0 specification, therefore, eventually it will take maximum advantage of GPU-accelerated programs. AMD “Carrizo” APUs contain 3.1 billion of transistors, 29 per cent more than “Kaveri”, but its die size is similar to that of the predecessor, whereas its power consumption is significantly lower. To archive that, AMD had to use a number of tricks.

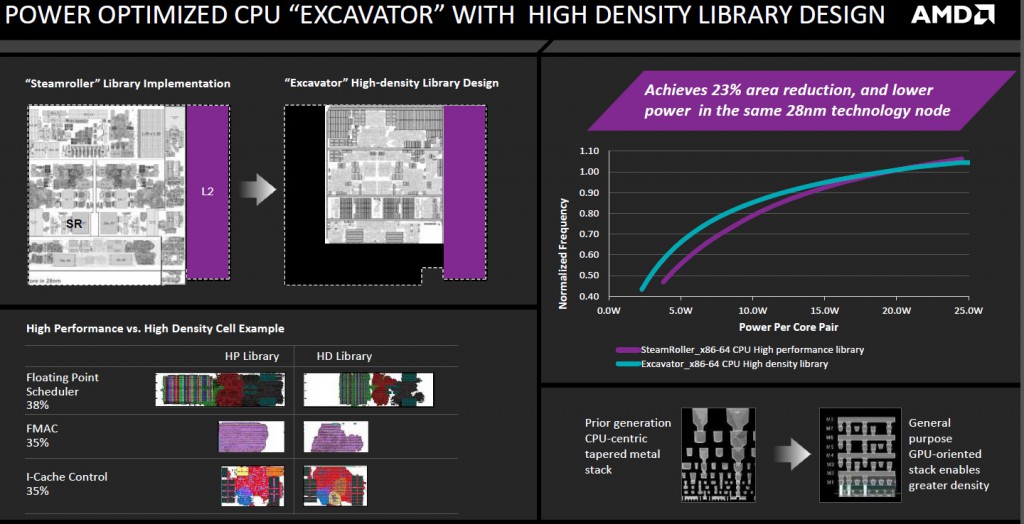

Although both “Kaveri” and “Carrizo” are made using 28nm process technology, the former relies on GlobalFoundries’ 28SHP (28nm super high performance) fabrication tech that is designed for the highest clock-rates. In a bid to enable extreme frequencies, high-performance chip design libraries decrease transistor density, which results in bigger chips. While it is unknown which process technology is used to make “Carrizo”, it is known that AMD used high-density chip design libraries (HDL) for the chip. According to the company, usage of high density libraries and automated design methods (akin to those used for graphics processing units) helped the company to reduce sizes of “Excavator” cores by 23 per cent compared to “Steamroller” cores inside “Kaveri” and reduce their power consumption by whopping 40 per cent.

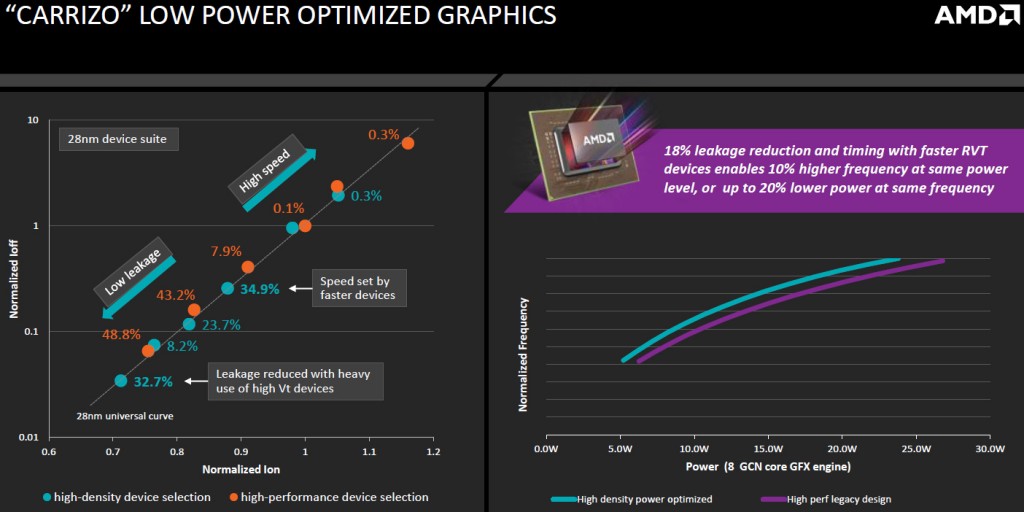

Usage of high-density libraries and automated design decreased the number of metallic layers inside “Carrizo” from 13 to nine, which also helps to cut-down power consumption and reduce leakages. Moreover, according to AMD, it used more high Vt transistors for the GPU part of the accelerated processing unit to reduce GPU power leakage and therefore reduce power consumption of the whole chip. This is not something really surprising since high VT transistors have always been used for mobile GPUs in general, only this time we are talking about far heavier usage of them in certain parts of the APU.

Design methodology, high-density libraries and possible transition to a different fabrication process are not the only things that AMD has done to cut down power consumption of “Carrizo”. The new APU is the first in a series of hybrid chips that contain a number of technologies designed to make microprocessors more energy efficient.

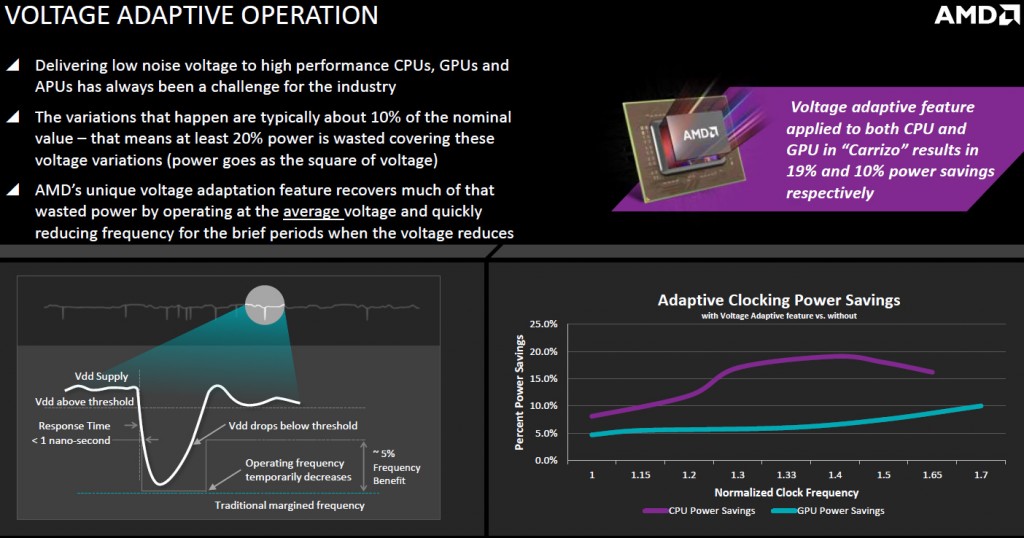

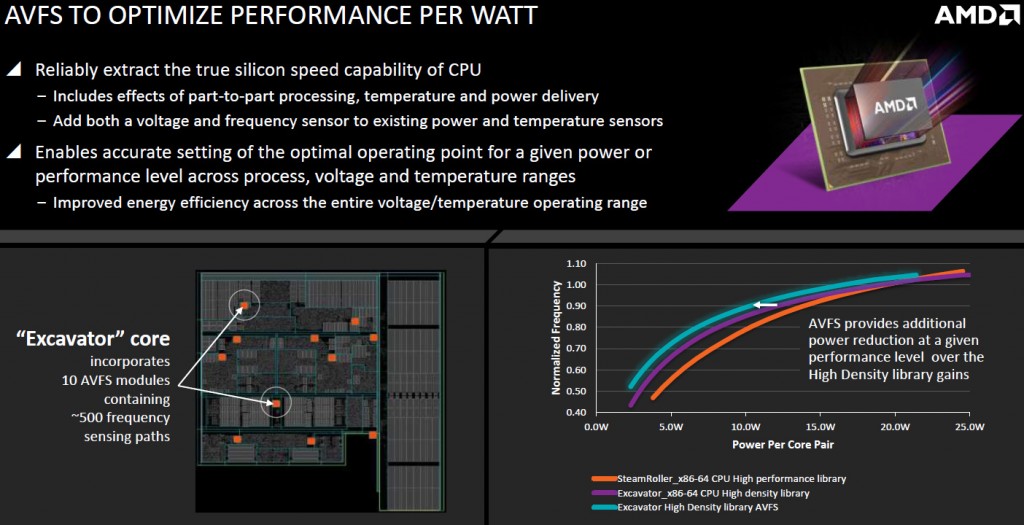

First of all, “Carrizo” incorporates voltage adaptive operation, or, adaptive voltage and frequency scaling (AVFS), which, when applied to both CPU and GPU in the APU results in 19 per cent and 10 per cent power savings respectively. AVFS modules (there are ten of such modules per “Excavator” core) monitor various aspects of chip’s condition (temperature, voltage, etc.) to adjust frequency and voltages in real-time. Essentially, AVFS reduces the typical operating voltage for a given frequency by adapting to per-part and environmental conditions, which reduces leakage and active switching power. While AVFS hardly brings a lot of benefits at high TDPs, the technology helps to reduce consumption at relatively limited thermal envelopes at given performance. In short, “Carrizo” will show its best at 15W – 20W. The chip itself is unable to work at extreme frequencies and AVFS will not provide advantages at 30W and beyond.

Another innovation that will reduce power consumption of “Carrizo” based notebooks is a new S0i3 power state, which achieves the same power level as the S3 state (standby), but without requiring intervention of the operating system, which means that it can be activated on the fly under the control of power management at sub-second time frames. While this may not dramatically reduce power consumption, it clearly makes the APU less power hungry.

While the density of integration and drastic measures to improve power efficiency of “Carrizo” are nothing, but impressive, when it comes to pure performance, not everything is that rosy. The “Excavator” x86 cores deliver only 5 per cent higher IPC compared to “Steamroller”. While the cores got smaller and more power efficient, this is a result of usage of HDL, AVFS and automated design. Despite expectations several years ago, the “Excavator” continues to have a weak floating point unit (FPU) consisting of two 128-bit FMACs, which are considerably slower than Intel’s contemporary 256-bit FPU. Therefore, even if AMD decides to create a high-performance design with “Excavator” cores, such chip will hardly deliver competitive performance since the amount of performance-related improvements compared to “Steamroller” seems to be limited. While the “Carrizo” may be a great APU for low-power mobile devices, it will not scale beyond that market. Therefore, if you demand high performance from AMD, wait for the company’s new “Zen” micro-architecture to arrive in 2016. However, if you want an AMD-based ultrabook or 2-in-1, “Carrizo” is a great thing to look at.

Thanks to maximum integration, AMD “Carrizo” should help notebook makers to simplify their designs and cut-down their costs. Since “Carrizo” is pin-to-pin compatible with lower-cost “Carrizo-L”, this will also increase flexibility of laptop platforms. That flexibility translates into lower prices, but not necessarily into thinner and sleeker chassis, but AMD needs to just retain its share on the market of notebooks, not bring breakthroughs. Therefore, it will not be a problem for the company if higher-end “Carrizo” ends up in chassis designed for lower-end “Carrizo-L”.

In general, AMD’s “Carrizo” looks like an interesting APU. The developer seems to pin a lot of hopes on heterogeneous system architecture (HSA) capabilities of the platform to deliver required performance to applications that really need it. In fact, AMD has pinned most of its hopes on HSA-enabled programs for a while now, which is why it has not really tried to address performance issues of “Bulldozer”, which were evident to it back in late 2010. The advances that AMD has made with its “Carrizo” show that the company still can improve its microprocessors, which is a good thing in general.

Discuss on our Facebook page, HERE.

KitGuru Says: The big question is how competitive will AMD’s “Carrizo” chips be against Intel Corp.’s chips with similar power requirements. To be precise, which 15W – 20W system-on-chip will be faster in real-world applications. That’s the question that we will be able to answer in the coming months, when AMD finally releases its “Carrizo” chips commercially.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards