Intel Corp. is working on a brand-new server platform code-named “Purley”, which will include Xeon microprocessors based on the “Skylake” micro-architecture with up to 28 cores and will feature a number of platform-level innovations. The new multi-core chips will not only sport extraordinary amount of cores and new features, but will also get physically bigger than today’s chips, making server infrastructure considerably more complex.

Intel “Purley”: Biggest platform advancement in a decade

The “Purley” platform will be Intel’s biggest server platform advancement in many years, when the world’s largest chipmaker rolls it out in 2017. Intel’s “Purley” will be a highly-configurable platform designed for enterprise, cloud, HPC [high-performance computing], storage and network applications. Intel “Purley”-based supercomputers are expected to finally hit ExaFLOPS performance late this decade.

The platform will support dual-socket (2S), quad-socket (4S) as well as octa-socket (8S) machines and will rely on Intel’s next-generation a point-to-point processor interconnect UPI (Ultra Path Interconnect) bus, which will replace the company’s current-gen QuickPath Interconnect (QPI) technology.

At present, not a lot is known about Intel’s next-generation UltraPath Interconnect (UPI) technology (also known as KTI or Keizer Technology Interconnect), except the fact that it will operate at 9.6GT/s or 10.4GT/s data-rates and will be considerably more efficient than today’s QPI since it will support multiple requests per message.

The “Purley” server platform will be the first to support six-channel memory per socket, which will provide massive amount of bandwidth to each processor. Besides, the new platform will also be the first to support Intel’s OmniPath 100Gb/s fabric to connect for external compute and I/O nodes, which will greatly increase performance in supercomputer applications.

Intel Xeon “Skylake”: 28 cores, 6-channel DDR4 memory, Omni-Path fabric

Intel will release three different versions of Xeon processors for its “Purley” platform targeting different applications two years from now – “Skylake-EP”, “Skylake-EX” and “Skylake-F” – according to a report from CPU World. The new chips will feature up to 28 cores based on the “Skylake” micro-architecture with AVX512 instructions and Hyper-Transport technology, up to six DDR4 memory channels (up to two 2400MHz DIMMs per channel are supported, i.e., up to 768GB of DDR4 memory per socket without SMB), up to 48 PCI Express 3.0 lanes as well as two or three UPI channels per socket.

- Intel Xeon “Skylake-EP” processors will be aimed at mainstream dual-socket (2S) servers and will thus only have two UPI links. Thermal design power of low-power versions of such processors will range from 45W to 80W, whereas standard high-performance offerings will have TDP of up to 145W. Workstation-class offerings with increased clock-rates will be rated to dissipate up to 160W.

- Intel Xeon “Skylake-EX” processors will be designed for high-performance and mission critical machines with two, four or even eight sockets, which means that they will feature up to three UPI links. The processors will introduce new RAS [reliability, availability, serviceability] features such as Instruction Retry (pipeline error protection for integers), Advanced Error Detection and Correction as well as Adaptive Dual Device Data Correction, to make next-gen high-end servers even more robust. According to previously released unofficial information, Intel’s forthcoming expandable processors will support four times higher memory capacity (compared to today’s chips) thanks to “Apache Pass” scalable memory buffer (SMB), which means up to 6144GB (over 6TB) per socket, or up to 24576GB of DDR4 RAM per 4S machine. The “Skylake-EX” chips will have TDP of up to 165W.

- Intel Xeon “Skylake-F” will be aimed at high-performance computing applications (which use 2S platforms) and will incorporate one link of the first-generation OmniPath fabric with 100Gb/s bandwidth. The latter will be supported by the code-named “Storm Lake” chip, which will be incorporated into the Xeon’s multi-chip-module (MCM) package. Among other things, Omni-Path Fabric will be used to connect to next-gen Xeon Phi co-processors.

Thanks to massively higher memory bandwidth, increased core count, improved micro-architecture and 512-bit AVX-3.* instructions, expect Intel Xeon “Skylake” processors to offer dramatically higher performance compared to today’s central processing units for servers. The architecture of the processors will be configurable, hence, Intel will easily tailor it for custom solutions required by its large cloud datacentre clients. Moreover, the new processors are expected to integrate “Cannonlake” graphics cores and media transcode capabilities, at least, optionally.

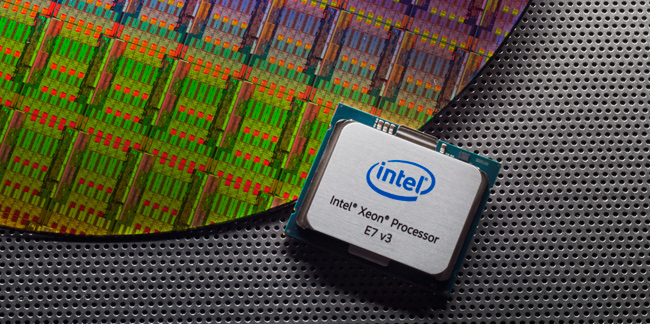

Intel socket P0: Big CPUs need big sockets

Since the new chips will feature more memory channels, integrated fabric and will be considerably more complex than today’s server microprocessors, Intel will introduce all-new infrastructure for its “Purley” platform.

The upcoming Xeon “Skylake” processors will use the new socket P0 and will feature flip-chip land-grid array packaging (FC-LGA) with up to 3467 contacts. The final amount of pins to be used is unclear today, but according to unofficial information, it will exceed 3000 balls.

The dimensions of the new Xeon processor packages will also be considerably larger compared to today’s LGA2011-3. Intel is currently considering 76mm*51mm or 76mm*56mm sizes, CPU World claims. By contrast, today’s Core i7 Extreme and Xeon E5/E7 chips in LGA2011-3 form-factor feature 58.5mm*51mm component size. Mainstream Intel LGA1150 processor come in 37.5mm*37.5mm packages.

Since packages are going to be used by several generations of chips, Intel has to include support of features for future generation processors.

Intel C620 “Lewisburg”: Massive I/O for massive servers

Intel “Purley” platform will rely on the company’s new C620 “Lewisburg” chipset, which will sport massive amount of improvements compared to today’s C602J and C610 platforms.

The top-of-the-range C620 “Lewisburg” core-logic will use four DMI 3.0 lanes (8GT/s) to connect to CPU and will support four 10GbE ports, 20 PCI Express 3.0 lanes, 14 Serial ATA III ports, 10 USB 3.0 ports, a new Intel QuickAssist accelerator as well as all-new Intel Innovation Engine.

The new QuickAssist accelerator is expected to provide substantially improved acceleration performance: up to 2.5x faster decryption, and up to 4x better compression speed compared to “Coleto Creek” chip used today.

The new Innovation Engine promises to enable server makers to create their own custom remote management solutions and no longer rely solely on Intel’s own Active Management software. The IE is based on a dedicated 32-bit x86 core, which means that it will be rather powerful.

Intel is expected to release its “Purley” platform and Xeon “Skylake” processors in 2017.

Intel did not comment on the news-story.

Discuss on our Facebook page, HERE.

KitGuru Says: Without any doubts, Intel’s “Purley” platform will be nothing, but a breakthrough. What is noteworthy is that it will not support PCI Express 4.0, as expected several years ago; integrated silicon photonics and some other things. Nonetheless, when all features of the new platform from Intel are considered, it is obvious that with “Purley” the world’s largest maker of CPUs will again strengthen its positions in the market of servers.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

yass! just what i needed to play minecraft!

Might need to try some overclocking, not sure there are enough cores to handle it! Lol

no PCI Express 4.0???

As long as each voxel has its own core and set of socket pins I think the clocks can be kept pretty modest.

Actually KitGuru blocked comments on that YouTube videos after a number of people abused the sysytem and restorted to insults. The idea is we engage in adult debate and conversation.

Just like you they hid behind pseudonyms.

Here’s a thought – why don’t you post using your real name? also, you may wish to look up the word ‘ranting’ as you clearly do not know what it means.

Well, noone said anything about YouTube, only you just did. I said about the discussion on your website with discus accounts. You deleted so many posts….

Anyway, what’s done is done. It’s pity. And sad !!!!!

You were talking about ‘a video’. And the reason you post anonymously is?

You have posted a gazillion videos on your website, that doesn’t make KitGuru YouTube, right?

Anyway. I’m all done with your biased opinions. Take care, have fun and keep doing whatever makes you happy. Oh, and delete any comments you like, it’s your site.

My name’s George if that makes you happy.

You lost a reader.

Obviously you are welcome to read or watch what you like George. So which country are you from and what is your connection with AMD? If you are merely an extreme and opinionated fan then fair enough but do you have a commercial connection with AMD?

Honestly saying i don like this intel only ecosytem smells evil…. 95% share in intels hand …hats off intel guyz

I’ll play crysis

Are you sure it will support Hyper-Transport? Didn’t you mean Hyper-Threading?

the first? ARE YOU OUT OF YOUR MIND! you’ll need like a supercomputer!

Yup bro ….i need ibm upcoming 120 petaflop super computer ,, then i sit on chair nd enjoy crysis……wooopie

The irony is that 20 years ago, the power of a modern low-end PC for nothing but Youtube was a supercomputer in the form of a couple tens of thousands of first gen Pentiums at 60MHz or so.

So 20 years from now, whatever media streaming service in VR 3D or whatever will need the power of modern supercomputers today.

Can’t tell if it is lazy programming or an utter waste of compute cycles for the sake of “pretty”.

amd needs to make 16 core consumer chip on intel ipc level. That would make intel so mad. Profits lost. Cant sell crappy quads anymore. At this pace well be stuck with quads for a decade.. and people are in content with that.

Planned for 2017 and still no USB 3.1 support on the chipset? Seems strange to adopt USB 3.0 but not 3.1.

Yeah, because parallelism is so easy and useful. That’s why Bulldozer was such a huge hit right?

i was thinking more along the lines of async compute. ofc cpus dont have so many cores which would warrant something so good. Lol. quads been here since 2006? Still most games utilize 1 thread. Whos fault is that.