Advanced Micro Devices has confirmed that it is researching a multi-core accelerated processing unit based on “Zen” micro-architecture, which will eventually power supercomputers with extreme performance. At present the company is only considering a concept design and it is unclear when AMD decides to actually develop such processor.

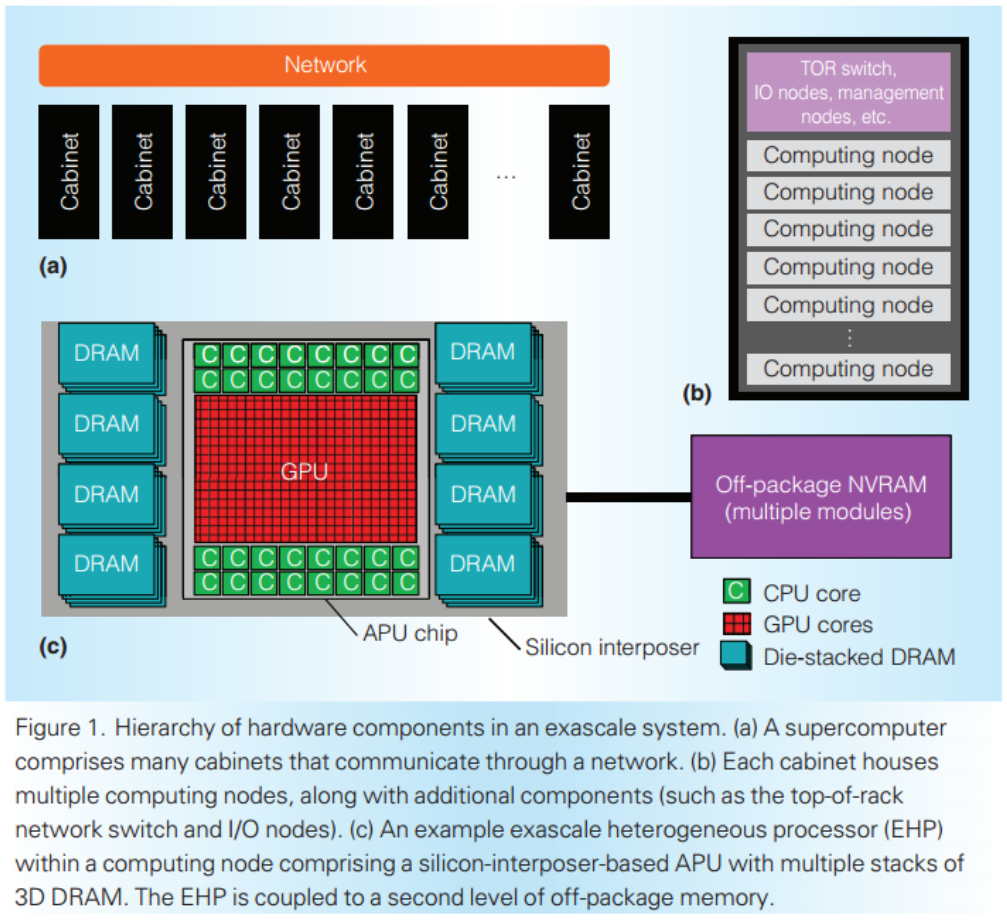

AMD, just like many other leading designers of chips, believes that supercomputers with exascale-class performance will have to use hybrid processor that feature both general-purpose cores as well as multiple stream processors found in graphics processing units. AMD has been promoting the idea of hybrid accelerated processing units since 2006, hence, its vision regarding “exascale heterogeneous processor”, which it outlined in a paper published by IEEE, is not surprising.

“To make fully realize the capabilities of the GPU, we envision exascale compute nodes comprised of integrated CPUs and GPUs (i.e., accelerated processing units or APUs) along with the hardware and software support to enable scientists to effectively run their scientific experiments on an exascale system,” the paper reads. “We discuss the hardware and software challenges in building a heterogeneous exascale system, and we describe on-going research efforts at AMD to realize our exascale vision.”

BitsAndChips web-site reports that the concept of EHP [exascale heterogeneous processor] features 16 or even 32 general-purpose cores based on “Zen” architecture, stream processors based on the next iteration of GCN [graphics core next] architecture as well as HBM [high bandwidth memory].

Earlier this year first details about 16-core APU leaked. AMD’s EHP for supercomputers is expected to feature 16 x86 “Zen” cores with two-way simultaneous multi-threading technology and 512KB L2 cache per core, 32MB L3 cache as well as a new-generation “Greenland” graphics engine with ½ double precision compute rate. The exascale heterogenerous processor is also projected to feature a quad-channel DDR4 memory controller with enhanced ECC capabilities that supports up to 256GB of memory per channel, 64 lanes of PCI Express 3.0 that can be used for SATA Express, integrated SATA, 1GbE, USB as well as various legacy interfaces. The APU is also expected to feature on-package 16GB of HBM2 memory with 512GB/s or higher bandwidth. It is assumed that the chip will hit the market in 2017, but AMD has never confirmed this.

AMD confirmed development of a datacenter APU earlier this year, but has never revealed its specifications. Keeping in mind that initial processors based on “Zen” micro-architecture will be made using 14nm FinFET process technology and will not feature more than eight cores, chips with 16 or 32 cores will likely be manufactured using 10nm FinFET fabrication process sometimes in 2018, at the earliest.

Discuss on our Facebook page, HERE.

KitGuru Says: The new paper released by AMD formally confirms what the company has been talking about for years. It does not mean that the company is actually developing an APU with 32 x86 cores and a GPU engine. However it does confirm the company’s vision regarding the future of server chips.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards