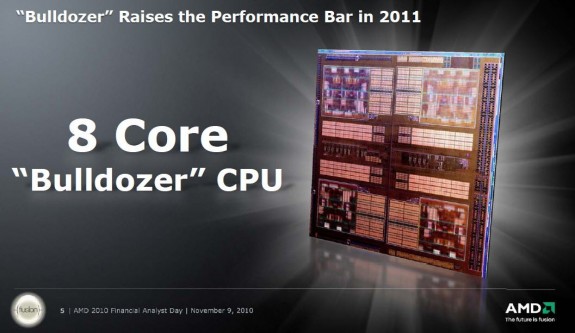

It looks like AMD has a class action lawsuit on its hands over the company's Bulldozer series of processors. The complaint stems from claims that AMD overstated the number of cores contained in the chip, the lawsuit says that while AMD advertised Bulldozer as having eight cores, it only really had four, due to the unique design, which combined functions of what would be two discrete cores in to one module.

Each module on Bulldozer is seen as two separate cores within Windows. However, the cores share a single FPU, along with the same instruction and execution resources. Intel CPUs on the other hand feature a different design with independent FPUs.

The lawsuit (via: Ars Technica) goes on to claim that due to this design, each core is not capable of working independently, which apparently results in performance degradation. The main point here seems to be false advertisement, as not everyone will understand the inner-workings of a CPU and would trust AMD to provide correct specification details.

These are all pretty serious allegations, which would put AMD in violation of the Consumer Legal Remedies Act in the US. The plaintiffs in the case are seeking statutory and punitive damages from AMD. You can find a summary of the lawsuit, HERE.

Discuss on our Facebook page, HERE.

KitGuru Says: A lawsuit like this will likely take a couple of years to come to a conclusion, so we could be hearing about this for a while. Do any of you think that AMD misrepresented the core count on its Bulldozer CPU?

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

The lawsuit is ridiculous. The Judge doesn’t define what is and what is not a core. Scientists/engineers do.

AMD Bulldozer family uses conjoined cores, whose concept was introduced in the literature years before by the academic people advancing computer science. The paper in question is “Conjoined-core Chip Multiprocessing” by Kumar et al and published in IEEE Micro on year 2004. Conjoined cores are adjacent cores that share some “topologically feasible resource” to reduce “die area with minimal impact on performance and hence improving the overall computational efficiency.”

AMD is not the only has used conjoined cores. Sun engineers once developed an architecture with each pair of cores sharing one FPU and clusters of four cores sharing the fecht unit.

The irony here is that the concept of conjoined cores was introduced by researchers at the department of Computer Science and Engineering University of California, and this ridiculous lawsuit is filled on a California court.

its one of the many faults with our judicial system today. you’ve got people completely uneducated in the topic they plan to rule on making decisions as if they’re all knowing. sadly there’s no good solution.

I think my only problem with this lawsuit is that it is a few years late. Were the plaintiffs just naive and oblivious of the reviews done early on over the modules and cores and whatnot?

Except there is not anything as true cores and false cores. Bulldozer module uses conjoined cores, which are so real as any other physical core.

CMT is not another form of SMT. CMT and SMT are completely different techniques with different goals different strengths and weakness.

That patent is for a power control mechanism, not for Bulldozer. The core diagram showed here is used for illustration purposes for the power control mechanism. Nowhere in that patent it is said that diagram is Bulldozer and in fact since it is used for illustration purposes the doc mentions different configurations with different number of clusters, FPUs, threading mechanisms, and even non-x86 ISA. In fact AMD was working in an ambitious project which was originally expected to be K10, but was canceled, never finished, and later modified and transformed into Bulldozer. That original project lead by Andy Glew used a cluster architecture like that where both clusters could run the same thread using a SpMT mechanism.

The definition of Bulldozer architecture, and the module concept was given by AMD engineers (including the chief architect) in the paper “BULLDOZER: AN APPROACH TO MULTITHREADED COMPUTE PERFORMANCE”,

Intel doesn’t use conjoined cores. Intel uses CMP cores. Atom uses clustering to simplify the hardware and reduce SS/OOO complexity.

This is nothing other than a smear campaign against AMD with the launch of Zen on the horizon.

Intel advertises its i7’s as a quad core with 8 threads. It’s not advertised as an 8 core CPU.

Traditionally, a whole single core consists of integer processing circuitry, a scheduler, and a floating point unit. AMD’s chips share the scheduler and floating point unit between cores. It’s not far fetched to say that since they cannot operate without the shared components, they are not truly individual cores. You don’t put two cars bodies on the same wheels and call it two separate cars now do you?

It’s pretty simple logic, and just because one might want to be lazy about the distinction, doesn’t mean the distinction isn’t there.

While many people know the design of the bulldozer architecture, not everyone does, and in fact, no one should need to do research to figure out if the CPU they buy/bought has the full amount of cores or some design trickery. There definitely needs to be a solid definition of what a CPU core is, otherwise it could get ugly in the future.

Fact is, if they had 8 true cores without shared components, there would be a performance difference…a drastic one at that. For example, core for core, the Phenom II architecture is faster than the FX series at the same clock rate….it’s just that the FX has the benefit of smaller fabrication and higher clock. That alone speaks volumes.

And it was in that AMD patent where the first glimpse of AMD’s CMT

design layout (which was the basis of AMD’s Bulldozer desgin). Furthermore those (integer) clusters are for dedicated hardware threads execution, but were never real cores by themselves. The actual physical core is the “module”. Even though AMD’s engineers changed all those terms for those parts later (just to suit AMD’s marketing IMHO), the point still stands that the original terms shown in the early design was correct. Thus it was never anticipated early in that design stage that these parts would require any sort of “correction” (by changing “cluster” to “core” and “core” to “module” before submitting the patent). Additionally using AMD’s own definition of what a “dedicated core” is, then AMD’s previous CPU architectures like K8 and Barcelona literally has 3 “cores” internally https://upload.wikimedia.org/wikipedia/commons/d/d6/AMD_K10_Arch.svg Note that they have 3 groups (or clusters) with each one containing both scheduler and ALU+AGUs together. And that is main issue, labelling these clusters as “dedicated cores”.

I suppose the judge is going to understand the technology enough to render a rational decision. Yeah, right. Whatever. I have 6 core and each core works great and I see it on my xfce4-cpugraph-plugin app. Looking forward to the Xen!! 😀

If you are talking about this https://www.eecis.udel.edu/~cavazos/cisc879-spring2008/papers/conjoining_micro04.pdf then those cores mainly only share the caches and FPU only. Each core’s main components are all intact, because each have their own front ends (e.g. instruction prefetching and decoders), thus they are full fledged cores. The main crux of this design is the cache controller which has to handle instruction fetch request from both cores. Sharing too many components between cores simply dissolves the boundary between a real core and a SMT configuration. When there’s only a single front end between “cores” to feed the execution threads, then that is already in SMT territory. In other words, a real core should have its very own instruction fetch mechanism, otherwise it will cease to function.

Here’s another analogy. Its like two motorcycles sharing a single fuel pump and a single gasoline tank. However those two motorcycles cannot be independant, and have to travel together (cannot be separated). That’s characteristic equals to a single motorcycle having two engines and 4 wheels, and certainly not like two individual motorcycles. How about Intel’s core analogy? More like a car, has a single engine and 4 wheels.

Since none of us paid a whole lot for our 4 module 8 cores to begin with, what will this lawsuit do for us? Get us a discount on a discounted CPU? Nope… The lawyers win! They get paid because one figured out how to reverse patent troll and make a buck. Who loses? AMD does, we do of course. Competition will be shunted less choices, more price gouging. Yay Frivolous shoulda been done 4 years ago Lawsuit!

So scientists and engineers do judge / make laws nowadays? Paradise for technocrats!

Bulldozer has a shared prefetcher actually

single engine, 4 wheels, and drive 2 for heavy pulling 😉

But on top of that, advertising 8 cores is kind of worse because AMD does have competition. If the competition all of a sudden starts branding stuff 2x what it actually is, you have some unfair competition, and as big as intel is, it did lose business to this 8 core nonsense, both to fan boys and to people who might assume more cores = better overall, when in actuality 8 AMD ‘cores’ can’t keep up with 4 intel cores.

Summary of that analogy: have two engines but working as a single vehicle. IMHO Intel welcomed it because its free PR, especially when reviews show that AMD’s “8 cores” can be beaten by Intel’s 4 cores (beating to the drum of “Intel uses only half the number of cores to beat AMD” subliminally). Thus Intel didn’t lose much business at all (but perhaps lost a very miniscule percentage to hardcore AMD fans, plus un-informed early adopters and average joes). Those who were well informed and kept up with CPU technology certainly aren’t fooled by AMD’s “8 core” claims. The plaintiff seems to fall outside of that, which resulted in his dis-satisfaction.

Similar analogy from http://www.neowin.net/forum/topic/1277716-amd-face-lawsuit-after-falsely-advertsing-the-number-of-cores-in-their-chips/ quote…

“Car Salesman “Oh this beauty has 2 engines”

Average Joe “Oh so that means it’s twice as fast with both running and you can shut one off to conserve fuel?”

Car Salesman “Well, no they both have to run at the same time all the time, and they run together and do not run independently”

Average Joe “So, there’s really only 1 engine in here then…”

Car Salesman “Umm…. yeah.””

That prefetcher is singular at the “front” (reading from the cache) but shared at the “back” (distributes both threads’ instruction stream)…

We have to realize that while we’re in the know about computer hardware specs, most people aren’t. Most computer owners don’t even know how to format their hard drive, and even when people do know, that doesn’t mean they have a good grasp of hardware specs.

Many people equate more of any number to better/faster. There are people who still think that an 8 core AMD is faster than any intel quad core…or even nearly as fast.

I would say that a good chunk of AMD sales are stolen from Intel because of the whole 8 core symbolizing more power. I think many people would have went Intel if they had realized the truth. Being misled by false advertising is not the consumers fault, even if we think they should have known better….the truth it, it’s impossible to always know better. One shouldn’t have to look in depth when purchasing. When I buy a car for example, I don’t typically look at the horsepower or max RPM’s or the configuration of the engine and make a decision based on that.

Also, even though I’m in the technical know, when I buy hardware I typically don’t do anymore research on it or discuss it. So issues or facts could come to light, and unless I accidentally come across that information, I’m not going to know that I got screwed.

Intel doesn’t use conjoined cores. Intel uses CMP cores with SMT. Intel only can advertise as octo-core the 8T/16 core i7 extreme chip.

Traditionally cores didn’t have FPUs, in any case it is irrelevant. Did you read the literature cited? Did you even bother to read the definition in my post? Conjoined cores are not “truly individual cores” because, by definition, they share resources with adjacent cores.

It is not about being lazy, it is not about advertising, it is about being precise and technical and know the terminology in the field. Some people can continue repeating the typical Intel fanboy claim that are not “true cores”, but there is nothing as true or false cores in the field of engineering or computer science and the concept of conjoined cores is well-established in the paper mentioned.

You confound the concept with the illustrative examples. The definition of conjoined cores is already given in the abstract of the mentioned paper:

The definition only mentions sharing resources between adjacent cores, it doesn’t say what has to be shared and what not. The authors of the article studied different configurations where different elements were shared (floating-point units, crossbar ports, instruction caches, and data caches). This doesn’t forbid AMD engineers from coming with another configuration for Bulldozer/Piledriver, which also shared fetch and decode… and another for Steamroller/Excavator, sharing fecth but not decode (SR/XV modules have two decoders).

In fact, Sun engineers proposed still another configuration with pair of cores sharing one FPU

unit and clusters of four cores sharing the fetch unit. Their design is described with all detail in the paper “ROCK: A HIGH-PERFORMANCE SPARC CMT PROCESSOR” published in the same journal.

If you read the paper about conjoined cores, you can see that the authors mention that conjoined cores are somewhat in the middle between CMP and SMT. The boundary is diffuse in the extremes because there is a continuum of different kind of cores.

You can continue repeating non-technical claims about “real” and “false” cores, but I have provided you technical information (three papers) that shows you are plain wrong.

The concept of conjoined cores was published before Bulldozer was released. You don’t seems to grasp that a patent is a legal document only for purposes of litigation with other companies to save R&D efforts. It is still more amazing you accuse AMD engineers changed the terminology to adapt to AMD marketing, not only without any proof, but deliberately avoiding that the terminology of CMT core was available on science/engineering since year 2004.

K7/K8K10 are ordinary clustered architectures. The concept of clustered architectures is even older in the field of computer science than the concept of conjoined cores. You have no clue.

Traditionally each core has its own front end, and traditionally a core using SMT technology has a single (shared) front end also, example: IBM Power8 http://www.extremetech.com/computing/181102-ibm-power8-openpower-x86-server-monopoly That’s has been the perception of standard CPU core arhitectures. Furthermore if companies like AMD were to use variations of SMT technology marketing them as “cores” then the true meaning of a CPU core will soon be lost (and also in dispute). Classic example titled “Sun UltraSPARC Rock: When is a core not a core?”: http://www.cpushack.com/2015/01/16/sun-ultrasparc-rock-when-is-a-core-not-a-core/ even the article’s author questions Sun’s definition of their “core”, quote “Each 4-core cluster shared a single 32KB Instruction cache, a pair of 32KB Data caches, and 2 floating point units (one of which only handled multiplies). This type of arrangement is often called Clustered Multi-threading. Since floating point instructions are not all the common in a database system, it made sense to share the FPU resources amongst multiple ‘cores.’ ” (note the emphasis on ‘cores.’ just like I used “cores”). Further quote “This should sound familiar, as its also the basis of the AMD Bulldozer (and later) cores released in 2011. AMD refers to them as Modules rather then clusters, but the principle is the same”. Thus if those variations of SMT technology (including CMT) can be marketed as “cores” then it becomes free-for-all, even Intel could have called their Pentium Extreme Edition 840 (the first desktop 2C/4T CPU: http://techreport.com/review/8285/intel-pentium-extreme-edition-840-processor ) as the first desktop “quad core”!

Here’s a simple analogy: having only just an engine does not equal to having a working vehicle, likewise having only two engines still does not equal to having two working vehicles. An engine is still an engine, and doesn’t do any work until its installed into a vehicle (like a motorcycle or a car). You can install 2 engines into a single vehicle, but it is still a single vehicle. Let’s look at another (correctly labeled) diagram of Bullddozer for comparison…

https://upload.wikimedia.org/wikipedia/commons/thumb/e/e9/AMD_Bulldozer_block_diagram_%28CPU_core_bloack%29.PNG/586px-AMD_Bulldozer_block_diagram_%28CPU_core_bloack%29.PNG

Note the integer clusters, then compare to AMD’s marketing slide presented by their engineer concerning “dedicated cores”…

http://www.techpowerup.com/img/10-08-25/bulldozer-8.jpg

Just like I’ve expected, AMD’s FX series CPU “cores” SMT-like behaviour was in the lawsuit claim http://regmedia.co.uk/2015/11/06/amd_bulldozer_lawsuit.pdf on page 13, example task manager screenshot…

http://img.techpowerup.org/130622/bta213006.jpg

Well, not much to worry about lost sales as Intel have other channels and (non-PC) market segments (e.g. servers, embedded, etc) where they can sell their chips to. An example for embedded market: http://linuxgizmos.com/com-express-type-6-module-revs-up-to-3-2ghz-core-i7/ which requires low TDPs. And I don’t think Intel had worried much about AMD’s “8 core” chips, as Intel lately had never spoken nor mentioned about AMD much at all (as a competitor), unlike the old days (for example: http://www.alphr.com/news/home-and-leisure/125411/intel-dismisses-amds-triple-core-challenge ). Even if AMD has sold lots of FX series CPUs, their margins are razor thin or none at all (due to expensive SOI, large die sizes and lowly pricing). That’s why AMD is still suffering earning losses. Thus that is AMD’s number one issue, their margins are practically too low. And even with Sony’s PS4 and Microsoft’s Xbox1 on board, AMD still continue to suffer losses…

Just because intel is still going strong, doesn’t mean what AMD has done is excusable nor does it mean it exempts AMD from consequences. I could for example, attempt to murder someone….just because I didn’t succeed or do well doesn’t mean there wouldn’t be consequences.

Agree with you that the management and bad decisions has cost AMD dearly. For example, rewards should not be given while the company is in financial turmoil (example of a recent debacle: http://www.bloomberg.com/news/articles/2014-11-25/advanced-micro-shareholder-sues-over-new-ceo-s-stock-grant-1- ). Going for SMT would be easier, as only minor parts (e.g. register files) needs to be duplicated (for 2nd thread), while the rest are scheduling tricks (to serve 2 threads). Thus the core die size does not increase much at all, for example http://www.anandtech.com/show/2658/8 quote “In the Pentium 4 days enabling Hyper Threading required less than a 5% increase in die size but resulted in anywhere from a 0 – 35% increase in performance.”. Before embarking on Bulldozer project, AMD should have learnt from Sun’s CMT failure, example titled “Sun UltraSPARC Rock: When is a core not a core?”: http://www.cpushack.com/2015/01/16/sun-ultrasparc-rock-when-is-a-core-not-a-core/ quote “Each 4-core cluster shared a single 32KB Instruction cache, a pair of 32KB Data caches, and 2 floating point units (one of which only handled multiplies). This type of arrangement is often called Clustered Multi-threading. Since floating point instructions are not all the common in a database system, it made sense to share the FPU resources amongst multiple ‘cores.’” and quote “This should sound familiar, as its also the basis of the AMD Bulldozer (and later) cores released in 2011. AMD refers to them as Modules rather then clusters, but the principle is the same”. Synonymous with AMD’s Bulldozer’s plight http://www.alphr.com/news/enterprise/357943/larry-ellison-slams-suns-astonishingly-bad-decisions quote “This processor had two incredible virtues: It was incredibly slow and it consumed vast amounts of energy”…

‘Traditionally’ cores didn’t have FPU until someone introduced FPU inside a core. ‘Traditionally’ cores didn’t have cache until someone introduced cache. ‘Traditionally’ cores couldn’t execute 2,4,8 or more threads at once, until someone invented SMT cores… Traditionally’ cores’ didn’t share front-end or the FPU or the L1 cache or the crossbar,… until the concept of conjoined cores was introduced in 2004.

IBM power 8 uses SMT cores not conjoined cores. As explained to you before CMT is not a variation of SMT, but something completely different. It is also explained in the IEEE paper I gave you but yo refuse to read. It is explained in the abstract that conjoined cores are a core configuration in the middle between two extremes: SMT and CMP. Thus it is explained in the IEEE paper and also in late in marketing material from AMD that CMP < CMT < SMT regarding sharing.

There is not anything like "the true meaning of a CPU core". I already explained you why, but you insist on non-technical motivations. I provided you a peer reviewed paper on IEEE journal. By some strange reason you believe that an anonymous page on a personal website is the equivalent of specialized peer-reviewed top literature, but is not. Moreover, a simple reading of the website shows that the anonymous author doesn't know the stuff. He claims that Alpha 21264 is the first chip that introduced the CMT concept, but he is plain wrong. The Alpha 21264 was a simple clustered architecture, where the integer part was broken into two clusters to avoid a bottleneck from a bigger unified integer register file. The article about the Alpha 21264 was published in IEEE journal in year 1999. The CMT concept was introduced latter, in the 2004, in the same journal. He is wrong and anonymously inventing stuff, just like you are.

A analogy is a similarity between like features of two things, typically for the purpose of explanation or clarification. It is not an identity and it is not a definition.

Science and engineering aren’t developed by appealing at car analogies. They are using scientific methods, logic, and so on. The concept of conjoined cores is established in the specialized literature. You can look for different analogies and some will support the concept and other don’t depending of how close and accurate is the analogy that tries to represent the concept. Your use of false analogies is a well-known logical fallacy. A more accurate analogy would be that of conjoined twins. There are two persons not one. But again concepts in science and engineering are not introduced by analogies (which are always imperfect by definition). Concepts are introduced via definitions. And I already provided you the engineering definition of conjoined core.

Except that “conjoined cores” paper does not mention anything about front end sharing. That’s the main point I’ve previously stressed, quote “traditionally each core has its own front end, and traditionally a core using SMT technology has a single (shared) front end also” because that falls into SMT territory. Referring back to http://www.cpushack.com/2015/01/16/sun-ultrasparc-rock-when-is-a-core-not-a-core/ quote “The idea of CMT, however, is not new, its roots go all the way back to the Alpha 21264 in 1996, nearly 10 years before the RK. The 21164 had 2 integer ALUs and an FPU (the FPU was technically 2 FPUs, though one only handled FMUL, while the other handled the rest of the FPU instructions) . The integer ALUs each had their own register file and address ALU and each was referred to as a cluster. Today the DEC 21264 could very well have been marketed as a dual core processor”. He’s referring to those two clusters, which today AMD markets them as “cores” (exactly as described in my replies earlier). Let’s compare SMT and CMT….

Similarities.

– both SMT and CMT uses shared (instruction) cache

– both SMT and CMT uses shared front end

– both SMT and CMT uses shared FPU or FPU cluster

Differences.

– SMT uses shared execution resources between threads

– CMT uses dedicated execution resources for each thread

Thus CMT actually has more similarities to SMT. As mentioned earlier, CMT is simply another form/variation on SMT technology. Can we still call those CMT threads as “cores”? Heck, no! They are exactly like SMT threads, and even behaves like SMT threads http://www.tomshardware.com/reviews/windows-7-hotfix-bulldozer-performance,3119.html quote “Arun says that the dual-core modules have performance characteristics more similar to SMT than physical cores, so the company is looking to detect and treat them the same as Hyper-Threading in the future”. Here’s the main problem, if the operating system treats them like real cores then can expect performance degradation.

In the early days, the cache was also external and optional, starting from Intel’s 80386: http://www.tomshardware.com/reviews/intel-cpu-history,1986-3.html thus also was not part of the main CPU core originally. However nowadays that cache has already became an integral part of any CPU core, especially when it comes to enhancing performance. Also in the early days, the FPU was external and optional (as a plugin upgrade), thus was not considered as part of the main CPU core. Intel’s 8087 http://www.cpu-world.com/CPUs/8087/ was one of the first FPU co-processors for IBM PCs and compatibles. Just like the cache, nowadays people expected that FPU to be “part and parcel” of a core. You can read the plaintiff’s complaint about dedicated FPU per core here http://regmedia.co.uk/2015/11/06/amd_bulldozer_lawsuit.pdf from page 10 onwards. Same goes with L2 cache, already very much integral part of any core nowadays (cannot be separated, unlike the optional L3 cache). The closest thing to “conjoined cores” IMHO is Intel’s Conroe, where both (full fledged) cores share a single L2 cache. You can still argue that Intel’s Conroe is closer to CMP but with shared L2 cache…

Putting two engines (sharing the gasoline tank and fuel pump) into a single vehicle does not make two vehicles, likewise putting two integer execution clusters into a single core structure does not make two cores. You can put many more engines into a single vehicle, but it is still a single vehicle. For most people, its not hard to see my analogy…

Engine = Integer execution cluster (AMD’s “core”)

Vehicle = Main core structures including front end and cache (AMD’s “module”)

Sharing the gasoline tank and fuel pump = Shared cache, front end and decoder.

My use of analogy is way better as it can be analogous to both AMD’s Bulldozer and Sun’s Rock “multi-core” architectures…

The Paper gives the definition of conjoined papers:

It is evident that two adjacent cores sharing front-end fulfill the definition, like it does cores that don’t share the front-end but share another part. Even admitting you have difficulties with logical thinking and can get to the conclusion by yourself, you could check the MPR article about Bulldozer: “Conjoined Cores Cut Cost in Next-Generation CPU”.

Rest of you post is a new repetition of the same flawed arguments, false claims, and the same links with wrong information (cpushack) that you have been posting in different sites and that have been conveniently corrected two, three, or even more times. You can repeat the same flawed arguments and link to the same wrong sites forever, that you will not change anything.

You are repeating wrong stuff was corrected before.

The two cores in each module can’t operate independently, and that is one of the main points the plaintiff is making. There are 8 “cores,” but they can’t act as 8 cores.

That Linley paper? http://www.linleygroup.com/newsletters/newsletter_detail.php?num=4008 That company puts out lots of dubious PR material, especially famous for IBM’s hypothethical performance claims and marketing comparisons. They are more of a PR and marketing company nowadays AFAIK. As mentioned earlier, by sharing a front end, that’s no longer in the territory of real cores but more in the territory of SMT-like configurations. Seems you are the only one that has never questioned how far can “conjoined cores” go, without stepping into SMT territory. Because you disagree with authors of those sites who questioned those “cores”, and you call them “wrong”? Perception-wise, besides myself, there are still many people who does not see them as real cores.

There are no corrections, nor any corrections required on my side. I have laid down the basics, while you still continue to peddle that “conjoined cores” paper.

I guess you are confounding them with a site humorously named inteltech has just published a laughable review of Power8, but don’t try to divert attention. You have not provided a single valid argument still. You only ignore the corrections to your posts and repeat the same flawed arguments again and again or simply misrepresent others’ arguments (a classical logical fallacy).

As explained in the IEEE paper mentioned before, the cores in a CMT-based chip can be accessible via software as any other core. The FX-8000 CPU can run 8 independent threads at once. The only difference with a CMP design is that the performance is reduced due to sharing some resources between pair of cores. But AMD cannot be sued by that because (i) the concept of conjoined cores is explicitly based in the reduction of performance by sharing resources to increase efficiency and reduce die area –read the definition– and (ii) AMD did it clear in the marketing and promo material that performance is a bit reduced compared to CMP. Sure you heard about the ~20% module penalty. I did and plenty of people around the world did as well. The guy that filled the ridiculous lawsuit may be the only person in the world ignorant of this fact.

https://scalibq.files.wordpress.com/2012/02/3663732_9bc35365d1_l.png

The concept of conjoined cores is at the center of this issue. The concept is well-established in the specialized literature on computer microarchitecture and it is only a pair of people from outside the field that makes incorrect claims or fills silly lawsuit.

I have already provided counter arguments but you’ve never accepted them (claiming “flawed arguments”), and even others (like the author at CPUShack Museum) also had the same perception as me (AMD’s “cores” are really clusters). Not everyone buys AMD’s “cores” claim, example: http://blog.stuffedcow.net/2014/01/amd-modules-hyperthreading/ quote “AMD’s marketing department did a good job convincing most of the world that a thread context that delivers only 54% more throughput deserves to be called a “core””. Seems that you are the odd one out. On that “inteltech” you must be talking about this http://www.anandtech.com/show/9567/the-power-8-review-challenging-the-intel-xeon- By calling them as such, you are trying to dismiss them as Intel paid reviews. Then how about Phoronix? http://www.phoronix.com/scan.php?page=article&item=runabove_power8_cloud&num=2 (link to results https://openbenchmarking.org/result/1410246-PTS-POWER8CL48 ) showing IBM’s Power8 being beaten by a single Intel Core i7-5960X most of the time. IBM had used Linley’s papers as marketing material, example: http://www-03.ibm.com/systems/power/advantages/smartpaper/memory-bandwidth.html (probably was sponsored by IBM also)…

The original paper http://rakeshk.crhc.illinois.edu/conjoining_micro04.pdf has never mentioned sharing the front end. If sharing the front end was a feasible part of “conjoined cores” then that would have already been proposed in that paper. However that was not the case, as it would dissolve the original (and traditional) cores. A “pair” of people (me and the CPUShack Museum author)? There are many others, example: http://linustechtips.com/main/topic/169565-is-amd-fx-8350-really-octa-core/page-7#entry2280146 quote “No. CMT is a design to duplicate the ALU cluster (which you call a integer core). CMT makes it possible to have 8 ALU clusters as a quadcore. You are starting to sound like people when HT (not SMT) arrived. “It cannot this, it cannot that, that is not how the regular designs works” and so on and so on. Again, I have atleast once said in this thread that the SIMD cluster is NOT a requirement. THE FRONTEND IS. THE BIG THINGY READING THE DATA AND TRANSLATING IT.”

You provided incorrect arguments, which I addressed multiple times, explaining why are wrong. You used the same flawed arguments on another site and another people corrected you again. You mentioned one anonymous author writing on a personal website like if that has same validity than peer-reviewed IEEE paper. I showed your anonymous author doesn’t know the stuff, because confounds conjoined cores in Bulldozer with the ordinary cores used on EV6. I know not everyone accept reality and facts. You don’t need to link to any personal blog in the world to prove that. You can also find crazy people on Internet that claims that Earth is flat and there exists a worldwide conspiracy by scientists, engineers, government,… to hide that.

Your credibility is just as questionable as any of those blog posts and websites (and this is the internet). Did you even check those sites’ personal information? Here’s one which I’ve used http://www.stuffedcow.net/ quote “Ph.D. Candidate, Dept. of Electrical and Computer Engineering, University of Toronto”. Then there’s the CPUShack Museum, and look his material http://www.cpushack.com/specs.html certainly he’s being following microprocessor technology for a long time. And he was well known in the computer industry. Example http://www.manufacturing.net/articles/2013/02/two-cpu-designers-who-changed-the-world quote ““On the original 8086 there was no way to context switch. You couldn’t run a multiprocessing OS on it,” said John Culver, who runs the CPUShack Museum. “Then Intel added protected mode on the 286 and 386 for multiprocessing. That’s how x86 and other architectures have morphed.””…

I am not giving myself as source, I am giving a paper published in a well-known journal specialized in the field, therefore your personal attacks are useless. If you knew a most elementary aspects about science and engineering you would be able to understand what references are reliable and what are not. A personal blog or an anonymous article on a website don’t qualify like a peer-reviewed top journal.

Even without knowing that, you would still be able to read the material provided to you, including the definition of conjoined cores, and get to the logical conclusion by yourself. But you are refusing to accept the obvious and looking for weird excuses like providing a snapshot of Windows resource meter like if that had some validity.

If you have some valid point was a repetition of stuff I answered/corrected before let me know.

Your problem is that you are trying to impose your views/opinions in your favor, while trying to dismiss other better viewpoints and data. I have shown that (besides myself) there are others that do not share your views/opinions. From another of my earlier reply, quote “The original paper http://rakeshk.crhc.illinois.edu/conjoining_micro04.pdf has never mentioned sharing the front end. If sharing the front end was a feasible part of “conjoined cores” then that would have already been proposed in that paper. However that was not the case, as it would dissolve the original (and traditional) cores.”.

The “traditional” basis for a core had never changed, which was a single (complete) processor. That includes all the components such as the front end (instruction fetch and decode), schedulers, registers, integer execution engine (ALUs), etc working together functioning on its own. Let’s look at AMD’s own public definition of cores http://www.amd.com/en-us/innovations/software-technologies/processors-for-business/multicore quote “With the power of two or more processors on a single chip, AMD’s true multi-core processors deliver industry-leading performance and unique features that help systems run cooler and more efficient”

Even Anandtech pondered about AMD’s “cores” http://www.anandtech.com/show/5448/the-bulldozer-scheduling-patch-tested quote “AMD wanted better performance than simple SMT (ala Hyper Threading) would allow but without resorting to full duplication of resources we get in a traditional dual core CPU. The result is a duplication of integer execution resources and L1 caches, but a sharing of the front end and FPU. AMD still refers to this module as being dual-core, although it’s a departure from the more traditional definition of the word”. Note that “integer execution resources” mentioned…

AMD’s CMT is not part of “conjoined cores” concept. The original paper http://rakeshk.crhc.illinois.edu/conjoining_micro04.pdf has never mentioned nor proposed sharing the front end. As I’ve mentioned much earlier, quote “AMD’s Bulldozer “cores” are not true cores but are technically called “clusters”…” Here’s the definition of CMT http://www.csl.cornell.edu/~albonesi/research.html#clustered quote ” In a Clustered Multi-Threaded (CMT) microarchitecture, the core is divided into smaller, more scalable, clusters, with communication paths introduced between them. Instructions from different threads are assigned to clusters according to a steering algorithm implemented in the front-end of the machine”.

According to Intel’s core definition https://software.intel.com/en-us/articles/frequently-asked-questions-intel-multi-core-processor-architecture#_Essential_concepts quote “Explained most simply, multi-core processor architecture entails silicon design engineers placing two or more execution cores, or computational engines, within a single processor package. This multi-core processor plugs directly into a single processor socket, but the operating system perceives each of its execution cores as a discrete logical processor with all the associated execution resources”. Especially the last part meant that Intel can count their HyperThreading “virtual cores” as cores. As menioned earlier, Intel could have marketed their Pentium Extreme Edition 840 http://www.tomshardware.com/reviews/pentium-d,1006-4.html as the first desktop “quad core” CPU. However Intel truthfully did not market nor advertise their HyperThreaded “virtual cores” as (real) cores.

Furthermore AMD’s CMT is not part of “conjoined cores” concept. Here’s the definition of CMT http://www.csl.cornell.edu/~albonesi/research.html#clustered quote ” In a Clustered Multi-Threaded (CMT) microarchitecture, the core is divided into smaller, more scalable, clusters, with communication paths introduced between them. Instructions from different threads are assigned to clusters according to a steering algorithm implemented in the front-end of the machine”. That core became “module” and clusters became “cores” in AMD’s marketing.

Unlike intell HT were u can only enable of disable. If you happen to have a REAL AMD AM3+/FX mainboard you should see something called CPU Core Control., Here you can have the follow options

One Core Per Comute Unit

Manual Enable or disable Modules,

Manual Enable or Dsiable Cores within A module

AMD FX are infact 8 Physical Cores

As stated just in the post you are replying Intel doesn’t use conjoined cores, thus their definition of cores is not the definition of conjoined cores.

The acronym CMT can mean different things to different people, just as SMT can mean different things to different people: (Simultaneous multithreading, Society for Music Theory, Sulfamethazine,…). We are here referring to AMD’s CMT and you are confounding it with the use of the acronym given by other people. The link you give refers to an ordinary clustering architecture, which is used in the EV6 that I mentioned before. That is not conjoined architecture.

https://en.wikipedia.org/wiki/SMT

https://en.wikipedia.org/wiki/CMT

I am not imposing opinions. I am posting information from reliable and high-quality sources, and correcting glaring mistakes/misunderstandings in your posts. The rest of your post is a repetition of arguments that I adressed before, including your misunderstanding of that Cornell page, which you posted above in another post and I just replied a pair of minutes ago. Go to the other post to see details on why you continue plain wrong.

You used that misleading argument before and I showed using the definition of conjoined cores why you are wrong. I don’t need to repeat the definition and the demonstration of why you are wrong. Moreover, this is the third time you mention the Cornell page in few hours. I corrected your new mistake in another post above. Again no need to repeat the correction here.

You used that misleading argument before and I showed using the definition of conjoined cores why you are wrong. I don’t need to repeat the definition and the demonstration of why you are wrong.

I was replying to this “Intel uses CMP cores with SMT. Intel only can advertise as octo-core the 8T/16T core i7 extreme chip”, which was not entirely true…

Now you’re using Wikipedia? Must be kidding right?

The definition is already very clear, even at that website. Especially the part “the core is divided into smaller, more scalable, clusters”. As mentioned earlier, AMD’s “cores” are really clusters. For further reading, can refer to his paper http://www.csl.cornell.edu/~albonesi/research/papers/ispass05_1.pdf quote “We choose a single monolithic SMT processor as a baseline against which to compare more viable approaches. In addition to the aforementioned CMP+SMT approach, we explore a partitioned SMT approach (P-SMT), a CMP of P-SMT processors (CMP+P-SMT), and a relatively new approach, a Clustered Multi-Threaded (CMT) processor. P-SMT is similar to Intel’s Hyper-Threading in that the issue queue resources used by a single thread are constrained, but with the additional complexity reduction of explicitly partitioning the issue queue. The CMT approach partitions/clusters the execution units and potentially the data cache as well” and quote “The primary difference between the P-SMT and CMT approaches is that the former assigns threads to execution units at issue time, while in the more highly partitioned CMT processor, this assignment is done at dispatch time by steering each instruction to a particular cluster.”

There are no corrections on my side, has never been. Very early on I have already mentioned AMD’s “cores” are really clusters, which is correct. In fact AMD’s CMT also has some similarities to P-SMT (Partitioned Simultaneous Multi-Threading), from the same site http://www.csl.cornell.edu/~albonesi/research/papers/ispass05_1.pdf quote “We choose a single monolithic SMT processor as a baseline against which to compare more viable approaches. In addition to the aforementioned CMP+SMT approach, we explore a partitioned SMT approach (P-SMT), a CMP of P-SMT processors (CMP+P-SMT), and a relatively new approach, a Clustered Multi-Threaded (CMT) processor. P-SMT is similar to Intel’s Hyper-Threading in that the issue queue resources used by a single thread are constrained, but with the additional complexity reduction of explicitly partitioning the issue queue. The CMT approach partitions/clusters the execution units and potentially the data cache as well” and quote “The primary difference between the P-SMT and CMT approaches is that the former assigns threads to execution units at issue time, while in the more highly partitioned CMT processor, this assignment is done at dispatch time by steering each instruction to a particular cluster.”

If you enable that “One Core Per Compute Unit” then its the same as disabling HyperThreading. Likewise can enable or disable cores on Intel CPUs also. AMD’s FX series CPUs do not have real physical cores. That “module” is the real physical core, while those “cores” are actually integer execution clusters.

AMD’s CMT is not part of “conjoined cores” concept. The original paper http://rakeshk.crhc.illinois.edu/conjoining_micro04.pdf quote “For the conjoined-core chip multiprocessor, we consider four optimizations – instruction cache sharing, data cache sharing, FPU sharing, and crossbar sharing” and quote “We add the additional constraint that the sharing is topologically feasible with minimal impact to a conventional core layout”. That’s why the paper had never proposed sharing other core components such as the front-end. As I’ve mentioned much earlier, quote “AMD’s Bulldozer “cores” are not true cores but are technically called “clusters”…” just as mentioned here about CMT definition http://www.csl.cornell.edu/~albonesi/research.html#clustered quote ” In a Clustered Multi-Threaded (CMT) microarchitecture, the core is divided into smaller, more scalable, clusters, with communication paths introduced between them. Instructions from different threads are assigned to clusters according to a steering algorithm implemented in the front-end of the machine”. That core became “module” and clusters became “cores” in AMD’s marketing.

First off the Modules are NOT the Cores.. This is the single number on mistake people make an information that people get or give regarding AMD FX chips

Second you u disable HT in intel all your disabling is the ability turn multi threads parallel on a single Core… Weather or not you disable HT still makes a I7 a quad core regardless etc

when u turn of a cpu ether individually, IE just 6, or 5 & 6, or 2-4-6-8 your actually disabling a CORE, OR I can disable entire Modules altogether

to make it more easy for you to under stand …

If I disable just core 8… the cpu becomes a 7 core chip. If I disable core 2 & 5 then the cpu becomes a 6 core. If I disable 1 core per a compute unit then it becomes a 4 core… if Go even feather and disable 1 Core per a unit and then disable 2 Units, Then it becomes a Dual core chip.

for any one that missed it again I say it one last time in CAPS

MODULES ARE NOT CORES, THERE A CLUSTER DESIGNE TO HOLD MULTIPLY PHYSICIAL (REAL) CORES

AMD sucks they make me sick. Intel…CRUSH!!!

That abitlity to enable and disable cores” does not mean they are real cores, as that is feature built into the processor (and controlled by BIOS). AMD’s FX series CPU “cores” are not (full feldged) cores but are (integer execution) clusters. From http://www.csl.cornell.edu/~albonesi/research.html#clustered quote ” In a Clustered Multi-Threaded (CMT) microarchitecture, the core is divided into smaller, more scalable, clusters, with communication paths introduced between them. Instructions from different threads are assigned to clusters according to a steering algorithm implemented in the front-end of the machine”. That core became “module” and clusters became “cores” in AMD’s marketing. That “module” is literally AMD’s (marketing) “invention”, because in most CPU core architectures you will not find this term assigned (to either their execution parts or entire core). Even in AMD’s patent http://www.freepatentsonline.com/20090024836.pdf that “module” is originally the physical core, and that “core” was originally a cluster…

https://uploads.disquscdn.com/images/96e6a2e4f0dcba7827dab0ad6a677bd3b7cc4130005c74008e5b4ed46060dde0.png

I am using wikipedia to show you that three letter acronyms can mean different things. You are confounding different CMTs. Cornell is not using CMT in the same sense than AMD on Bulldozer or Sun on the paper “ROCK: A HIGH-PERFORMANCE SPARC CMT PROCESSOR”. And what I said about Intel is accurate.

Three letter acronyms can mean

different things:

https://en.wikipedia.org/wiki/SMT

https://en.wikipedia.org/wiki/CMT

There are at least three different CMT on computer architecture: “Clustered Multi-Threaded”, “Cluster-based MultiThreading” and “Chip MultiThreading”. Cornell’s authors are not

using CMT in the same sense than AMD on Bulldozer or Sun on the paper

“ROCK: A HIGH-PERFORMANCE SPARC CMT PROCESSOR”. What Cornell authors call CMT is more close to the concept of CSMT than to AMD’s CMT.

Three letter acronyms can mean

different things:

https://en.wikipedia.org/wiki/SMT

https://en.wikipedia.org/wiki/CMT

There

are at least three different CMT on computer architecture: “Clustered

Multi-Threaded”, “Cluster-based MultiThreading” and “Chip

MultiThreading”. Cornell’s authors are not

using CMT in the same sense than AMD on Bulldozer or Sun on the paper

“ROCK: A HIGH-PERFORMANCE SPARC CMT PROCESSOR”. You are confused because you rely on combinations of three letters instead understanding concepts and definitions behind. What Cornell authors

call CMT is more close to the concept of CSMT than to AMD’s CMT.

P-SMT is just another technique with different motivation and goals than Cornell’s CMT and different to Bulldozer’s CMT or Rocks’ CMT.

Your misleading argument was corrected before at least two times: you take an example used only to illustrate the concept and ignore the definition of conjoined cores. The definition doesn’t say that the front-end cannot be shared, you can insist and insist forever, but we can read and use logic. Regarding Cornell paper three letter acronyms can mean

different things:

https://en.wikipedia.org/wiki/SMT

https://en.wikipedia.org/wiki/CMT

There

are at least three different CMT on computer architecture: “Clustered

Multi-Threaded”, “Cluster-based MultiThreading” and “Chip

MultiThreading”. Cornell’s authors are not

using CMT in the same sense than AMD on Bulldozer or Sun on the paper

“ROCK: A HIGH-PERFORMANCE SPARC CMT PROCESSOR”. You are confused because

you rely on combinations of three letters instead understanding

concepts and definitions behind. What Cornell authors

call CMT is more close to the concept of CSMT than to AMD’s CMT.

This discussion is about CPU technology and definitely that CMT is Clustered Multi-Threading, and not other unrelated “CMT” acronyms. Look at another AMD patent, this time on “MULTIPLE-CORE PROCESSOR WITH HIERARCHICAL MICROCODE STORE”: http://www.freepatentsonline.com/20090024836.pdf and again that “module” is originally the physical core, and that “core” was originally a cluster. Thus the definition from Cornell was correct all along…

https://a.disquscdn.com/uploads/mediaembed/images/2794/6278/original.jpg

This discussion is about AMD’s CMT technology and definitely that CMT is Clustered Multi-Threading, and not other unrelated “CMT” acronyms. In another AMD patent, this time on “MULTIPLE-CORE PROCESSOR WITH HIERARCHICAL MICROCODE STORE”: http://www.freepatentsonline.com/20090024836.pdf and again that “module” is originally the physical core, and that “core” was originally a cluster. Thus that definition from Cornell was correct all along…

https://a.disquscdn.com/uploads/mediaembed/images/2794/6278/original.jpg

This discussion is about AMD’s CMT technology and definitely that CMT is Clustered Multi-Threading, and not other unrelated “CMT” acronyms. Take a look at another AMD patent, this time on “MULTIPLE-CORE PROCESSOR WITH HIERARCHICAL MICROCODE STORE”: http://www.freepatentsonline.com/20090024836.pdf and again that “module” is originally the physical core, and that “core” was originally a cluster. Thus the definition from Cornell was correct all along. By misrepresenting what was essentially a cluster as a “core” is considered a deception…

https://a.disquscdn.com/uploads/mediaembed/images/2794/6278/original.jpg

Look at another AMD patent, this time on “MULTIPLE-CORE PROCESSOR WITH HIERARCHICAL MICROCODE STORE”: http://www.freepatentsonline.com/20090024836.pdf and again that “module” is originally the physical core, and that “core” was originally a cluster. Thus the definition from Cornell on Clustered Multi-Threading was correct all along…

https://a.disquscdn.com/uploads/mediaembed/images/2794/6278/original.jpg

Note the “computational engines” in their statement “… placing two or more execution cores, or computational engines, within a single processor package”, which can bypass the basic processor definition. Note “logical processor” in their statement “… but the operating system perceives each of its execution cores as a discrete logical processor with all the associated execution resources”. Simply said, “logical processor” equals an “execution core” there. Intel’s HyperThreading threads are perceived as a logical processor by the operating system.

That patent is not for Bulldozer but for microcode stuff and the diagram they use is here for illustrative purposes, and unsurprisingly it is the same diagram found in the other patent: copy/paste. The definition of Bulldozer architecture is given in the paper written by the engineers of the project.

As explained to you before, Cornells CMT is not AMD CMT nor Sun CMT. Intel’s HyperThreading is an implementation of SMT, which is a different technique than CMT.

This discussion is about AMD’s CMT technology and definitely that CMT is Clustered Multi-Threading, and not other unrelated “CMT” acronyms. Semantics aside, “Cluster-based MultiThreading” is the literally same as Clustered MultiThreading.

This discussion is about AMD’s CMT technology and definitely that CMT is Clustered Multi-Threading, and not other unrelated “CMT” acronyms. Furthermore “Cluster-based MultiThreading” is the literally same as Clustered MultiThreading.

http://a.disquscdn.com/uploads/mediaupload/tmp/56a163f02b3e664fa3a1c88f83146b3945db314c6d90939a1cca9f68/original.jpg

That diagram in AMD’s patent was the basis for Bulldozer, and I’m sure most people will instantly recognize the similarities. Each of those parts labelled (core and cluster) is exactly as described here http://www.csl.cornell.edu/~albonesi/research.html#clustered which is the basic fundamental principles and structure for CMT (as described in the paper)…

http://a.disquscdn.com/uploads/mediaupload/tmp/56a163f02b3e664fa3a1c88f83146b3945db314c6d90939a1cca9f68/original.jpg

Answered before.

Precisely AMD’s Cluster-based Multithreading is not the same than Cornell’s Clustered Multi-Threaded. I already explained you the differences multiple times.

This is a copy of a post I answered above. Check my reply.

This is a copy of a copy of a post that you wrote above and that I answered above.

It’s less of a question of the actual science, and more of marketing and common sense.

You can keep pointing out how scientists are always right, but you keep forgetting that we live in a capitalist world. Given enough money, it’s not that hard to claim that it’s a full core.

Now, here is the real issue though: common sense would dictate that an 8 core CPU brings 8x as much performance as a single core (or rather, 4x as much as a real 2 core). Bulldozer, no matter how shiny and well engineered it is, doesn’t bring that, and hence it is misleading. Those conjoined cores, at the end of the day, will have to wait for each other on the shared resources.

Calling them cores is a poor choice of word that is mostly done so for more recognition and for the sake of marketing by misleading people, and that is what the lawsuit is about.