Zen 4 Architecture Improvements

In the opening remarks delivered on-stage by AMD’s CEO – Dr Lisa Su – it was highlighted that the goal with Zen 4 had been to make the fastest core for gamers with the most compute for creators. The key areas in which they looked to tackle this goal were with the new Zen 4 architecture, TSMC 5nm manufacturing, the brand-new AM5 platform, improved IO with PCIe Gen 5, and better memory support with DDR5.

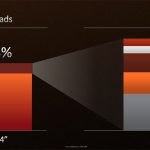

AMD’s performance goal for Zen 4 was estimated as 8-10% IPC uplift versus Zen 3. But this expectation was exceeded with a typical 13% IPC uplift as measured across a geomean workload of 22 games and content creation applications. Interestingly, the percentage uplifts versus Zen 3 aren’t all skewed towards content creation applications, either; there’s a clear trend of double-digit percentage point uplifts in gaming titles, too.

Mark Papermaster – AMD CTO and Executive Vice President – spoke of how the 13% uplift in IPC was achieved. The new front-end design was of notable importance and improvements to the Level 2 cache via its doubled size help.

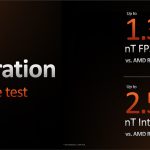

AVX-512 is now supported on Zen 4 to enhance the architecture’s abilities with respect to AI and Inferencing type workloads. This is implemented via a double-pumping of the 256-bit data width. AMD also claims up to 2.5x performance for nT Int8 Inferencing with AVX-512 VNNI vs Ryzen 5000 series.

A Watt-for-Watt efficiency comparison that AMD showed between Ryzen 9 5950X and Ryzen 9 7950X was interesting. The data shows up to 35% better performance on the new 16-core processor at 170W TDP. That stays roughly consistent at +37% for 105W TDP. But down at 65W TDP, Ryzen 9 7950X is up to 74% higher performance.

As is clear from the data – and as highlighted by Mark Papermaster – 65W TDP is where TSMC N5 shines.

But it’s not just the 4th generation FinFET technology process node itself that brings improvements such as an enhanced metal stack and better power efficiency. AMD has also leveraged its own design capabilities to offer those real-world efficiency gains by better leveraging the larger L2 cache and optimising high frequency and high density routing efficiency, for example.

Power efficiency improvements are probably about 60% due to the core and 40% from design techniques, according to Mark Papermaster. Mark also referenced AMD’s work to ensure that this chip is highly manufacturable with TSMC. That point is particularly relevant given Intel’s recent manufacturing struggles.

And another area that comes under the ‘efficiency’ umbrella is highlighted when looking at the comparative core specifications.

AMD’s new Zen 4 core manufactured on TSMC N5 measures 3.84mm2 when also factoring in L2 area. By comparison, Intel’s Alder Lake Golden Cove Core built on the Intel 7 Processor measures 7.46mm2 for Core + L2 area. SoC performance-per-Watt is also notably better for AMD, based on their own numbers.

Improving the process node upon which the Zen 4 IO Die is built (to 6nm) is another factor in the power efficiency equation. It was highlighted by David McAfee – Corporate VP and General Manager – how AMD’s learnings and power efficiency technologies that are implemented in the laptop CPUs are being brought into the desktop CPUs.

We also got a look at the CPU roadmap for AMD. Zen 4 with 3D V-cache will be coming, as will a Zen 4c design for applications where high frequency is not critical (i.e. server workloads).

And the grounds-up core design brought about with Zen 5 is on track for a 2024 launch.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards