Level 4 cache isn't commonly used on CPUs nowadays, but according to some findings, Intel wants to make it a thing again for the upcoming Meteor Lake SoCs. Using Level 4 cache is quite promising, as it should enable faster access times and improved boot optimization and security for the host CPU.

While details on the Meteor Lake implementation are scarce, the Linux patches indicated by Phoronix and a patent (via VideoCardz) filed by Intel in December 2020 shed some light on the potential use cases.

Data found within Intel's Linux patches points to the use of L4 cache and it working similarly to the eDRAM found on Broadwell CPUs like the Core i7-5775C.

As for the patent, it outlines a new SoC architecture that features on-package cache modules named Adamantine. These caches will be on the base tile and can be accessed by any of the building blocks of the SoC, promising to enable faster access times than typical caches like L3. These would improve boot optimization, increase security, and preserve the cache at reset for improved loading times.

Interestingly, the patent’s attached block diagram confirms that the Meteor Lake SoC will feature two Redwood Cove cores and eight Crestmont cores. On top of that, there are also two CMT cores in the SoC tile and Gen 12.7 Xe graphics with 64 EUs pictured in the diagrams.

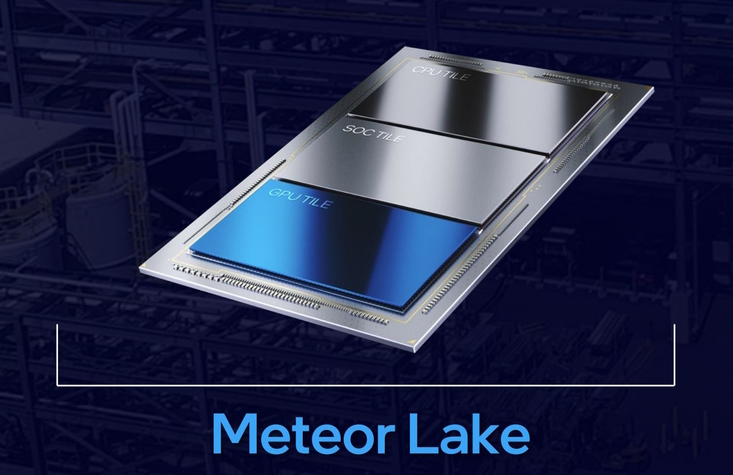

The hybrid architecture of Meteor Lake will incorporate five distinct tiles, namely CPU, SoC, GPU, I/O, and base tile. The company has not yet confirmed which Meteor Lake series will be introduced first, but they are still scheduled to release in H2 2023.

Discuss on our Facebook page, HERE.

KitGuru says: The return of a Level 4 cache promises exciting advancements in chip technology, and Intel’s patent suggests that the potential uses for the on-package cache are vast. We look forward to learning more about implementing the Adamantine cache in Meteor Lake and its impact on future chip designs.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards