Since the introduction of PCI 4.0 on AMD’s X570 platform, there has been a big push from manufacturers to have storage devices to support the new specification on the market for consumers to take advantage of the higher bandwidth and transfer speed it has provided.

Now that PCIe is established in desktop solutions we are hearing more details about the PCIe 5.0 interface and some manufacturers are starting to roll out products ready for the next generation of PCIe specification.

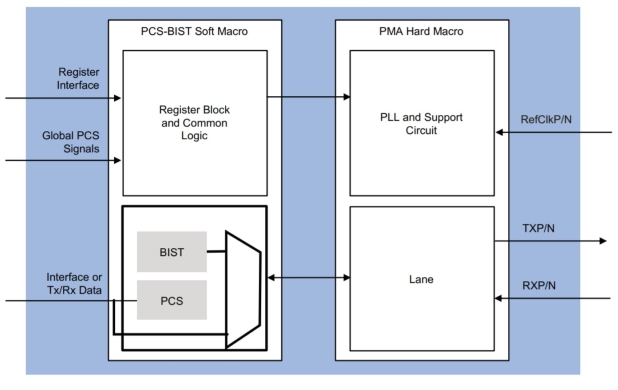

Rambus has announced today that it can now offer a comprehensive and optimised solution that is designed for PCI Express 5.0 and is backwards compatible with PCIe 4.0, 3.0 and 2.0. The PCIe 5.0 interface will include both PHY and a digital controller to provide easy SoC integration for quicker time to market. Rambus claims the PHY designed for 7nm node offers the best-in-class power, performance and area.

“Our high-speed SerDes and memory interface solutions make possible amazing advancements in performance-intensive applications in AI, data centre, HPC, storage and networking,” said Hemant Dhulla, vice president and general manager of IP cores at Rambus. “Now we’ve added PCIe 5 to our industry-leading portfolio of high-speed interface solutions giving chip makers another tool to unleash the power of their designs.”

Rambus recently acquired Northwest logic which provides the high-performance digital controller core for the new PCIe 5.0 interface. The PHY and the digital controller could be offered as either a fully validated and integrated solution or licensed separately to be used with a PIPE 5.2-compliant third-party solution.

Key features and benefits of the Rambus PCIe 5.0 interface include:

- Integrated and co-validated PHY and digital controller for complete interface solution

- Built with Rambus’ industry-proven design methodology for long-reach PCIe interfaces

- 32 GT/s bandwidth per lane with 128 GB/s bandwidth in x16 configuration

- Backward compatible to PCIe 4.0, 3.0 and 2.0

- Supports Compute Express Link interconnect

- Advanced multi-tap transceiver and receiver equalization compensate for more than 36dB of insertion loss

- Best-in-class power, performance and area

- Supports performance-intensive applications including AI, data centre, HPC, storage and 400GbE networking

The new Rambus PCIe 5.0 solution is available worldwide in an advanced 7nm FinFET process. further details of the Rambus SerDes solutions can be found on the official Rambus page.

Discuss on our Facebook page HERE.

KitGuru says: The introduction of PCIe 4.0 to desktop solutions has provided productivity users an excellent performance boost which helps reduce work times. PCIe 5.0 will offer double the data rate of PCIe 4.0 which in turn will provide further performance increases meaning users can access data even quicker.

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards