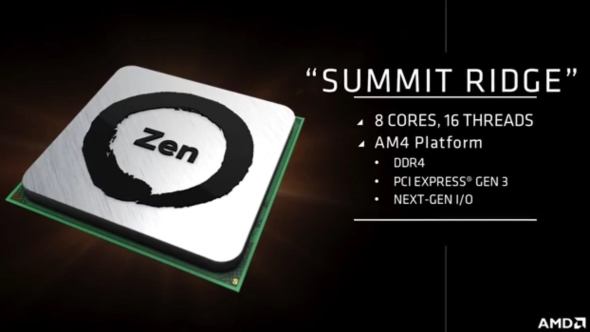

We have already heard a little bit about AMD's new AM4 platform, which launched just recently for OEMs. However, we have yet to see the socket on any high-end motherboards. Fortunately, if this week's reports are to be believed, we now have an idea of when to expect high-end AM4 motherboards with the X370 chipset, which will launch alongside AMD's new Zen processor.

According to a report from Benchlife this week, Socket AM4 will have three chipsets, ‘B350' and ‘A320' for low and mid-range boards, and X370 for the high-end. According to the report, motherboard makers are already stocking up on motherboards for all three AM4 chipsets and we may even see a few of these pop up in October.

However, the really exciting stuff will be showing up in January, likely at CES as AMD gears up to launch its first Zen CPU, which is said to be launching by February, alongside a slew of new motherboards.

Obviously, none of this information is confirmed or verified by AMD, so take this information with a pinch of salt. However, given everything we have been hearing so far about Zen's launch, it would make sense for it to hit store shelves in January/February.

Discuss on our Facebook page, HERE.

KitGuru Says: The official Zen launch window is still Q1 2017, which could mean anytime between January and March but hopefully it will arrive sooner rather than later. Are any of you guys holding out for Zen before upgrading?

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

KitGuru KitGuru.net – Tech News | Hardware News | Hardware Reviews | IOS | Mobile | Gaming | Graphics Cards

Yes I’m waiting but not necessarily for Zen. Either way it’ll be the best time to buy Intel or AMD because of price competition. (I am hoping for Zen though)

Me too. I was planning to compile a gaming desktop based upon AMD A10-7890K but now I’m holding up to see what price and performance can Zen offer. Plus, A10 is for FM2+ socket, so I won’t be able to switch to Zen nice and easy in case I buy an A10 at the moment; that is why I decided to wait for the next half a year.

Yes I am.

Yes , me too. My plan ( or hope ) is to get an affordable six core Zen CPU to upgrade my FX 6300.

I have this gut feeling that AMD is still hiding something other than the frequency and target market of Zen. It’s either something is stopping them with there certifications or are there bugs in the micro codes for the Zen chip/s.

Too late for the busiest season of the year. Sept to DEC. As usual if the launch is early next year. Amd is behind the 8 ball on more than just product developement.

There is no six-core Zen CPU. Only 95W 8-core and 4-core 65W models. I also doubt they will be cheap.

Yup, still holding onto my 2600K and Radeon 6950 until next August!

There will be six core chips.

There is only quad-core and octo-core engineering samples and official Zen roadmap only shows quad-cores and octo-cores. Where are the six cores?

I think the roadmap suggests 4-8 core chips, not 4 and 8.

Unless they’re gonna sell their 6900K-level chip for under $500, they’ll need to provide existing FX users an affordable upgrade path to Zen, likely an 8-core part with two cores disabled.

As stated there is no six-core samples only four and eight; and the roadmap doesn’t says “4-8 core” chips. It shows “8-core” and “4-core” CPUs but not six-core. Also there is no dual-core in the roadmaps. This seems related to Zen coming only in groups of four: what AMD calls a “complex”.

6 cores is a possibility, but only if AMD deems it necessary to release a 8 core model with a core disabled on each of the two modules/clusters, which could be a likely case depending on how well the fist yields go.

AMD has had to deal with a lot of re-structuring as well as other difficult things such as moving to a new node, so they’re being slowed down regardless.

Releasing in February isn’t so bad though as you can still get things like back-to-school sales depending on the country, additionally their carrizo AM4 APUs are being released before that.

That doesn’t mean there won’t be a 6 core product.

Not to mention the actual TDP of the chip itself. Certifications takes months to process and when you fail a certification, the chip will not be released or be validated to that certification like USB type – C certification must be able to handle data transfer at this level or bandwidth or if AMD claim the TDP is 45W and it exceed that it will loose its certification, like what happened to the reference RX 480 lost its PCI-e certification due to exceeding the 75W in the PCI-e slot.

It means no one, not even the people at AMD that makes the official roadmaps knows about the existence of those 6-core products that you imagine.

You cannot disable individual cores within a Zen complex, somewhat as you cannot disable individual cores within a Piledriver module.

Piledriver has granularity of one module, aka two cores: There is 2, 4, 6, and 8 core Piledriver.

Zen has granularity of one complex, aka four cores: There is only 4 and 8-core Zen. There is no six-core neither two-core Zen. Check the roadmaps.

If that’s the case then why did you say “There is no six-core Zen CPU”, how do you know there isn’t one?

Faulty 8 core products will have damaged cores disabled and be sold as 6 core products to recuperate as much profit as possible. They’re not going to disable perfectly working cores just so they can meet the quota of a roadmap and sell JUST 4 and 8 core products.

The gap between 4 and 8 core products is quite large in terms of available processing power and in cost, there’ll be 6 core products to fill the gap in the market for people who need more than a quadcore but something that costs less than an octocore.

AMD=Always More Delays….. as usual, even the mobo shown at the demo was still in prototypin stage, not reference design yet…. So chipset for HEDT not even ready….

I know all engineering samples are either 4-core or 8-core. I know there is no 6-core Zen in the official roadmaps.

You are assuming that faulty cores can be disabled independently, which is not not true. If you have a faulty core in Piledriver you have to disable the whole module (i.e. pair of cores). It seems evident that if you have a faulty core on Zen you have to disable the whole complex (i.e. four cores). My hypothesis explains why there is only 4-core and 8-core engineering samples. My hypothesis also explains why there is not 2-core Zen or 6-core Zen in the official roadmaps.

What are you going on about?

PCI-E certification is necessary because it’s an external standard, much like USB-C is an external standard, or a game console is an external standard.

AM4 is not an external standard. The criteria for passing are whatever AMD says they are. So if a chip doesn’t come out to 45W for example, they just say “this is now a 65W chip”. They don’t need any type of external certification.

There is some compliance involved, being whatever they told motherboard manufacturers they would be doing. But the motherboards are designed to handle a large range of chips, so the maximum wattage is probably at least 100 watts.

They will be made with defective six core chips.

Chips are traditionally never launched during Q4 (Sept to Dec). This is true for Intel as well as AMD. Chips launch earlier in the year, and then products using those chips launch later in the year.

This is why i just got the 6700k and a EVGA 1070FTW i always bought AMD but i just cant wait any longer for promises,The 8350 and 7970 will be handed down to a family member.

“You are assuming that faulty cores can be disabled independently, which is not not true.”

So why is there an option in the BIOS of AM3+ motherboards called “One core per Compute Unit”? If you can’t disable cores within the module without disabling the entire module then this option wouldn’t work, because it disables a core in each module so that the remaining active core can full access and control to what was once the shared segments of the module, leading to slightly better single threaded performance.

AMD have offered 3 core CPUs in the past which relied on binning the quad core CPUs with faulty cores, there’s nothing to say that they won’t do the same with Octocore products to provide Hexacore chips.

Any company that sells their product to the mass market can’t just say its good, a company can’t do that certification by themselves, it must be approves by a certified external source to approve the claims, if AMD or intel makes a mistake to their specs then the motherboard manufacturer will face the consequence and it will backfire especially this are CPU and not GPU, because CPU are always in-house and never done by AIB partners.

If it the chip is a 45W and failed due to it reaced 65W, they can’t just throw it and say it is a 65W chip, it must be processed if its reusable or not. AMD must not make any miscalculation on the chip, we don’t want another bulldozer chip and we need AMD to regulate this abnormal price tags on the hardware as we’ve seen today.

They’ve already done it with jaguar, and zen is mostly based off of it. The individual cores in both architectures are not dependant on each other like they are in the bulldozer series so individual cores can be disabled if required.

The real question is whether they would need to, which depends on yields and target prices.

There is no defective six-core engineering samples, and there is no defective six-core chips in the official roadmap. In fact there is no two-core chips either.

Some BIOS can do all kind of weird stuff even beyond official specs and tolerances. Now answer me why AMD is not selling 3-core, 5-core, and 7-core Piledrivers if disabling individual cores is so simple according to you?

Just because AMD offered a tricore in the past doesn’t mean it is doing it now. Microarchitectures change. There are three reasons why AMD will not offer any six-core now:

1) Zen is based in complexes of four cores each.

2) There is only quad-core and octo-core engineering samples. No six-core.

3) There is only quad-core and octo-core in the official Zen roadmaps. No six-core, neither two-cores.

Your assessment is perfectly reasonable, but it’s worth noting that even the 4 and 8 core parts aren’t even likely to be the same kind of chips. The 4-cores are almost certainly “Raven Ridge” APUs and X4s, distinct from “Summit Ridge” FX chips. We’re working on conjecture here, but there will likely be a significant gap in price and performance between 4-core and 8-core Zen that one would ‘reasonably expect’ to be bridged with an intermediate offering.

Jaguar is an ordinary CMP design with four cores sharing an L2 cache. And AMD disabled pairs of cores on it, i.e. there is only 2-core and 4-core Jaguar products but not 3-core as you pretend.

Zen is not based in jaguar. It is a “new design from scratch” and one of its characteristics is it is based in four-core complexes.

The argument of yields doesn’t work. It doesn’t make sense to sell a 4-core Zen die with half cores disabled, but not a six-core version. The reason why there is no six-core Zen has been stated multiple times before. It is the same reason why there is no two-core Zen in the mobile roadmap: Zen comes in multiples of four.

You raise some interesting points. Current engineering samples are CPUs. One is a 95W 8-core CPU and the other is 65W 4-core CPU.

http://cdn.wccftech.com/wp-content/uploads/2016/08/AMD-Zen-8-Core-4-Core-CPUs-Leaked.jpg

The roadmaps show 4-core and 8-core CPUs for desktop and 4-core APUs for desktop and mobile. I suppose the 4-core CPUs could come in two shapes: Raven Ridge with GPU disabled and Summit Ridge with one CPU-complex disabled.

Something similar happened before, you could purchase 4-core FX CPU for AM3+ (an octo-core die with 2 modules disabled) and 4-core Athlon CPU for FM2+ (a quad-core Richland die with iGPU disabled).

I agree that one would ‘reasonably expect’ an intermediate offering based in economic reasons. If you check some older posts from mine I was also expecting 8-core and 6-core Zen CPUs then. But now all is different: technical reasons (quad-core complex), existent engineering samples (only 4-core and 8-core), and official roadmaps (only 4-core and 8-core) says us convincingly that Zen dies come in groups of four-cores: there is no six-core; there is no dual-core.

@juanrga:disqus @paul17041993:disqus @yourma2000:disqus

I just want to mention that the roadmap slides indicate “up to 8 cores,” which is exactly how K10 was shown on its roadmap slides; “up to 6 cores.”

http://i.imgur.com/tcQszrX.jpg

http://images.anandtech.com/reviews/cpu/amd/FAD2009/desktoproadmap.jpg

And what happened there? We had II X4 chips made from II X6 silicon (Zosma), and II X2 chips made from II X4 silicon (Regor).

So while AMD may not explicitly announce dual-core and hexa-core processors, that doesn’t mean they won’t happen some time in the future. There’s no doubt that octa-core models will be available first as that’s the main focus for AMD, but history has shown that dedicated silicon usually follows silicon that’s partially disabled to create market segments that otherwise wouldn’t be there.

Intel has Celerons and Pentiums, and AMD isn’t going to use a quad-core Zen to compete against those. It would make far more sense that Zen use a dual-core with its SMT enabled; something Intel won’t do because it uses SMT to create further market segmentation.

Both Haswell E and Skylake were launched in August, so thats much closer to Q4…….

Take a good look at the block designs between jaguar and zen, they both have the same base design of a 4 core cluster with each core using a block of the shared L2 cache, with the exception that zen adds an additional layer to the cache, as L3, to increase the cache capacity and memory throughput to support SMT.

Jaguar’s base design was chosen simply because it’s extremely efficient and effective, it can even put earlier intel generations to shame despite using a node twice the size. Jag’s only downside is that it couldn’t clock well, much like ARM.

Interconnect tech between them CPU complexes is unknown. Could be ol’ ccHT, simple FSB like with shared NB, or ‘GMI’ bcoz usually AMD has 3 interconnects per CPU but Zen looks to have only 2 so already 1 could have been used internally….. Lookin at the distance between them L3 caches,interconnect delays is lookin inevitable…… Delays=Higher latency…… With a mem controller per CPU complex, tis Zen is lookin more like ol’ dual socket config.

I’m sorry, defective eight core parts would be used; not doing so would be a waste of resources.

Because to provide 5, 6 and 7 core products in substantial numbers you need A LOT of faulty octocore chips, and if yields are good then it’s not going to be possible unless AMD are willing to cripple perfectly good chips to meet the niche needs of the 5 and 7 core market, hexacore products at various clock speeds cover the vast majority of those niche performance areas.

As far as 3 core CPUs are concerned, the profit margins for tricore CPUs mostly likely are worth the effort of extra marketing and fragmentation of product catalogs, not to mention we’ve gone through a change that has seen quad core products become the norm for basic systems whilst anything less are rarely seen or are reserved for ultra low power systems.

“Just because AMD offered a tricore in the past doesn’t mean it is doing it now.”

We’re not talking about offering tricore products, we’re talking about offering hexacore products.

What happens when flagship desktop products reach 32 cores, do we start offering every possible core count between 1 and 32 just because we happen to have imperfect chips with certain #s of working cores? it’s not practical and only fragments the product catalog and makes marketing and selling the products more difficult. How do you market a 7 core CPU to someone when it doesn’t provide much more processor power over a 6 core chip and isn’t much cheaper than an 8 core?

If motherboard makers are capable if doing something you deemed as not possible and do it stably, then I think AMD themselves are capable of either disabling or cutting out defectives cores in a chip.

You’re looking at the old interconnect methods, AMD has multiple new ones, mostly via an interposer. Take note that the package the zen chip is on is also blue, which is quite new for CPU packages…

Every AMD CPU have at least 3 HT interconnects on die, that includes Faildozer and its successors. For servers all interconnects are exposed but for desktop only one interconnect is enabled. Them 12core and 16core Opterons used its interconnects for communications between 2 dies on MCM per socket, lookit http://image.slidesharecdn.com/vmworld2012rubensotonuma-120912144500-phpapp02/95/numa-performance-considerations-in-vmware-vsphere-6-728.jpg same config like Zen, each with its own cache and mem controller……. HT interconnects are designed for interfacin between 2 CPUs with own caches and mem controller…… ‘GMI’is supposed to replace HT…… Some dies have blue color also, so color is not indicator. Them CPU complexes are not on interposers but on a single die, so that should be much faster than interposers……. The problem is that the distance between CPU complexes particularly the L3 caches. Expect extra ns=nanosecond delays between L3 caches. Longer distance=more wire delays=higher latency. And if there is an interconnect like HT or GMI then latency further increases due to handshakin between CPU complexes when accessin each others cache or mem controller…… Lookit Intel 8core chip sample http://techreport.com/r.x/core-i7-5960x/die-shot.jpg their cores and caches are close together as a single unit, not split into 2 separate ‘CPU complexes’.

Intel’s L3 cache also runs quite slow and uses heaps of power because of its large complexity, additionally you’re talking about latencies the same as what many instructions operate, which is very small and especially compared to the actual memory latencies.

Also, if your code depends purely on the atomic performance of the cache then you’re just an idiot programmer, or need a _lot_ more experience and knowledge with threading…

The latency comes from handshakin between both CPU complexes when accessin each others cache and mem controller, which usually requires some sort of interconnect bus or protocol. Sample from QuadFX HT bus, lookit http://www.anandtech.com/show/2125/6 ‘With both sockets populated, memory latency goes up by around 27% and thus in applications that are more latency sensitive and don’t necessarily need all four cores, you get worse performance than with a single dual-core CPU. The added latency comes from the additional probing over the HT bus that’s done for coherency whenever a memory request is made to see where the latest copy of the data resides’

I just don’t think AMDs overturned all its cards to us yet, but, yeah, fair assessment.

Congrats by linking to a fake slide. In fact I was the first to show that Zen slide you use was a fake

http://semiaccurate.com/forums/picture.php?albumid=15&pictureid=37

Use Google to find the other fakes slides: https://www.google.es/search?q=Zen+fake+slides

Both are different.

Defective eight-core dies will be used for the quad-core CPUs.

You are the one that introduced tricores in the discussion, not me.

About why AMD and Intel are not selling 5-core and 7-core chips the reason is other. If you have tons of faulty dies with one core damaged the reason why AMD or Intel disable another core and sell a model with an even number of cores is just to balance the microarchitecture. It is the reason why there is no tri-core Jaguar, only 4-core or 2-core. It is the reason why there is no 5-core Piledriver, but 4-core or 6-core. It is the reason why there is no 17-core Xeon, and so on. And it is the same reason why there is only 4-core and 8-core Zen dies either in the hands of OEMs and in the official roadmaps.

You tried to imply I was talking about offering tricore products again by saying “Just because AMD offered a tricore in the past doesn’t mean it is doing it now” which I didn’t, I brought the Phenom II tricores up as example of a product that was not on the roadmap but was released regardless.

Also what do you mean “balance the architecture”? Again, the reason for the lack of 5 core and similar piledriver products IMO is down to lack of demand for such products and the undesirability of fragmenting product catalogs and marketing, same applies to the opteron products.

In regards to Jaguar APUs not having “tricore” products available, I think you’ll find that it probably has more to do with the amount of die size the CPU takes on those chips. If a chip were printed over a portion of contaminated silicon then it would more often then not affect part of the chip that isn’t a CPU core such as the GPU or integrated chipset, even if it did then that APU would be prioritized to be used as a dual core jaguar APU to fill the lower end of the ultra low power segment rather than bridging gaps. All that said, when you’re dealing with low performance chips of a few watts, people aren’t overly fussed for a chip that falls between something like the 5w dual core and 8w quad core.

We’ll just have to see, there will be 6 core products IMO, I don’t see why a buzzword like CPU complex should have any relation to what were modules on the Bulldozer class of chips when we have no information from AMD about the layout and structure of the chip, frankly that’s jumping the gun. there’s a segment in the market between quad and octocore products that is profitable and AMD knows that. Just because there’s no engineering samples of a 6 core product right now doesn’t mean there isn’t one, again going back to the Phenom II dual/tri core products, they never had engineering samples afaik.

You can call it fake all you like, but the fact remains the only thing that it’s incorrect about, is the socket, which was likely renamed anyway. Everything else was likely true at one point, but plans were changed by AMD, and that’s why they want to call it fake so no one is expecting something that never arrives.

Also, why were you banned from S|A?

But extremely similar and use 4 core clusters with partitioned shared cache.

As I already said;

“Also, if your code depends purely on the atomic performance of the cache

then you’re just an idiot programmer, or need a _lot_ more experience

and knowledge with threading.”

It’s called optimization, and for a start 90% of threaded workloads have no atomic dependency and are also working with datasets that would be in large,isolated blocks that would only have one or two threads operating on at a time each, ie; extremely low cross-core/cluster communication.

Also, why are you even bringing up a multi-socket platform from 10 years ago…? That’s just stupid as the technology has improved times and times over since then…

Bcoz one CPU complex=one CPU socket. You can’t split the L3 caches and mem controllers that far apart without havin some sort of interconnect or handsahkin in between. So what you said has nothin to do with the global latency problem them CPU complexes will face. Most desktop and games apps are not NUMA aware, and that QuackFX review clearly showcased that issue. Another sample http://techreport.com/review/11353/amd-quad-fx-platform/5 ‘It’s possible the FX-74 is hampered here somehow by NUMA overhead,’….. Larger datasets requirin access on another mem bank of another mem controller increases latency. Even L3 cache access between CPU complexes will incur some latency….. That ’10 year old tech’ is still in use today, in AMD’s Opterons server CPUs. Sample compare Interlagos http://browser.primatelabs.com/v4/cpu/228110 and MagnyCours http://browser.primatelabs.com/v4/cpu/83804 to leaked Naples bench http://browser.primatelabs.com/v4/cpu/105227 lookit the poor multi core scalin similarities. Those Interlagos are 2*8cores=16cores MCM per socket and MagnyCours are 2*6cores=12cores MCM per socket, all usin HT interconnects for chip to chip and also socket to socket. So single Naples most likely 4*8cores=32cores MCM per socket, usin either ‘GMI’ or HT interconnects.

My intention about tri-core was other. Just because AMD had in the past a microarchitecture with four or three cores doesn’t imply that any architecture can do the same. Take the example of Jaguar. There are four-core and dual-core, but not three core.

Modern microarchitectures as Jaguar, Zen, Piledriver, Haswell, etc. have a delicated balance of loads, signals, and even power. You cannot disable cores in arbitrary ways and sell the resulting chip.

You can continue to claim your opinion about a six-core Zen coming, but you didn’t address any of my remarks: (i) only quad-core and octo-core silicon exists now, (ii) the quad-core complex, (iii) no six-core appears in the official roadmaps, which only mention 8-core and 4-core chips, no “up to” but “8-core” and “4-core” chips.

Finally here you have some tricore engineering samples

http://www.cpu-world.com/CPUs/K10/AMD-Athlon%20II%20X3%202.6%20GHz%20-%20ZD260121K3216.html

http://www.cpu-world.com/CPUs/K10/AMD-Phenom%20X3%20-%201D170100J3BGA.html

https://www.techpowerup.com/84225/phenom-ii-x3-720-black-edition-tested

I can call them fake because are fake slides. It is also false that the only incorrect information is the socket. You are again inventing stuff to fit your narrative . The real slides with the official roadmap aren’t for 2016, there is no “up to”, “Basilisk” chip doesn’t exist, Bristol is lacking, there is no 2-Zen core APU, etc…, but well everyone except you have known for a while that the slide was fake. In fact, when I demonstrated that the slides were fake the author just emailed me giving me the congrats and explaining he did to show how easy was to fool people like you:

Thank you for bringing up the question about S|A, although I know your intention was other. I was given a temporary ban by “feeding the trolls”. It was completely unfair the mod banned me, but he didn’t ban any of the trolls. I took a screenshot of the mod message and the reason for the ban, and I have also a copy of another mod acknowledging that he was ready to ban everyone in the S|A forum except me. I will write about all this unfair stuff and will add mod correspondence and screen-shots, I didn’t decide still I will write about that. Of course when returning to S|A I will stop replying trolls, aka the 99% of posters in that forum.

The slides might have false information, but that doesn’t make them fake. As it so happens, AMD came out and proposed that they were fake. That’s the only real proof that they are fakes.

I covered Basilisk:

“Everything else was likely true at one point, but plans were changed by AMD, and that’s why they want to call it fake so no one is expecting something that never arrives.”

For what it’s worth, I had already seen your website and the slides months and months ago. A quick Google search however brings them back up, and they must have slipped my mind. I’m by no means weak-minded, thank you.

As for SemiAccurate, you don’t know my intentions so please don’t plant words into my mouth. I was actually wondering because I’ve been following that Zen thread for what can easily be four months now, checking up on any new posts from time to time (it’s stored in my bookmarks). I noticed one day that you were banned and haven’t seen you active around here until now.

I have been trying to contact the S|A forum staff to get myself registered so I can take part in the discussion, but no one seems to care. There hasn’t been one reply to any of my emails. Does S|A even care about its community?

I proved them to be fake, and latter AMD acknowledged them to be fake. I even received a email from the guy that invented them and give to you part of his email.

About S|A I remember you now. You are the guy said me having problems to join the forum

https://disqus.com/home/discussion/wccftech/amd_zen_cpu_shipping_in_limited_quantity_in_q4_2016/#comment-2802807277

Guess what? I emailed Charlie Demerjian last July and explained him your problem to join. I am still waiting for an answer. My belief is that they currently only care about subscribed people. That is why they banned me for “feeding the trolls” but didn’t ban the trolls. I am fully sure most of the trolls in the forums are subscribed and pay each month their subscription fee. Banning them means loosing money.

Except you already mentioned that both clusters are possibly on the same die, and just like the opterons the L3 caches are right next to each other, additionally it’s highly likely they’ll be using GMI, which would be vastly superior to HT especially for MCM’s, as there’s no reason to use HT any more.

You’re also greatly overlooking the inconsistencies of those benches and the fact that turbo is enabled on one of them, if you look at certain ones that actually matter for these systems, such as physics, they achieve full scaling across multiple sockets.

We’ve already talked about Jaguar, they’re low power chips with low performance, there’s barely any variance between dual and quad core parts in terms of power and performance compared to the gaps in performance of desktop products to warrant providing a 3 core part.

The article you linked to is in feb 2009, The Phenom II X4 appeared a month earlier in January and if there were eng samples of those I imagine they would’ve been available at some point in Q4 2008. You’re trying to make the point that because there’s currently only working quad and octo eng samples then that’s confirmation that there’s no hexa products to come.

Athlon II X4 = Sept 2009

Athlon II X3 = Oct 2009

Phenom X4 = Nov 2007

Phenom X3 = Mar 2008

Seems like a familiar trend that the full fledged chips are released first and when enough of those chips are binned down to lower tier products with less cores then eng samples are released along with official products soon after, which I’m saying is what will likely mostly happen with these Zen chips.

Again you keep bringing up the “quad-core complex” as if it has any certain significance, we don’t know how to layout of the chip affects the binning process at all, it might be stubborn as you predict but it also might be very flexible, so until more info is released by AMD then it’s a moot point to bring it up. I don’t think even AMD are stupid enough to release a product in which one fault amongst hundreds of millions or even billions of transistors can cripple 50% of the CPU.

As for the roadmap, here’s an official roadmap from AMD showing only quad core Phenom II parts for desktop products, no mention or hint to dual or tricore products for the desktop yet they went on to release them in Phenom II and Athlon II flavours:

http://images.anandtech.com/reviews/cpu/AMD/2008FADay/clientroadmap2.jpg

Your logic + this roadmap = Phenom II X2/X3 and Athlon II X2/X3/X4 never existed.

Oops, I missed that quote. Thanks for including his email. That guy proved a very good point.

I am that guy, yes. That would make sense, although it shows that they care very little about their community, on what is supposed to be a community forum.

MagnyCours do not have turbos, but still has the same poor multi core perf scalin. Them Zen CPU complexes are on the same die. But if you look at the Zen die, the split L3 caches amd mem controllers configuration is vastly different from Intel’s monolithic L3 cache and single mem controller. Even Bulldozer’s L3 caches are much closer together, clustered in the center of the die, also has a single mem controller, lookit….. http://cdn.wccftech.com/wp-content/uploads/2011/08/a5464735s.jpg

Your argument about power delta between quad and tri-core is not valid, because AMD is selling the same quad-core jaguar chip with 2.20GHz (Athlon 5370) and 2.05GHz (Athlon 5350). The power delta for 0.15GHz gap is smaller than between quad-core and tri-core. The reason why there is no tri-core Jaguar is other, as mentioned before.

It is irrelevant when engineering samples appear in the press. They are always fabricated before the first official chips. Your point was that no tri-core engineering sample existed and I demonstrated the contrary, twice.

My argument about the “quad-core complex” is about balance. It is unrelated to “the binning process”, making your point moot again.

You are assuming that AMD are not stupid enough to make stupid things, but history of the company suggests otherwise.

Finally the official roadmap that you bring means very little. That is a four year roadmap released in advance during a Financial Analyst Day. Ranging over a time span of four years, it lacks details (only discuss coarse details as node size memory type and die names) because it is only a guide for analysts and it is open to changes. The official roadmap I am mentioning is the one for OEMs, it is for the next year, and only for the next year and it was distributed only some few months ago.

What I know is that:

(i) The Zen microarchitecture suggests there is no six-core.

(ii) There is only quad-core and octo-core engineering samples.

(iii) There is no mention to any six-core in official roadmaps.

(iv) You didn’t address my points or did with invalid arguments.

I will continue saying that there is no six-core Zen. And you probably will continue saying there is one coming. If AMD releases a six-core Summit Ridge CPU I will admit my mistake. Will you do the same if Summit Ridge comes only in octo and quad-core configurations?

When my ban expires I will contact a mod to explain your case.

When my ban expires I will contact a mod to explain your case.

It costs me nothing to send a PM to a mod. Ban will be lifted next month.

That’s most likely down to 5350s not falling within the 25 watt TDP range at 2.2ghz, and are clocked at slightly less to meet the spec. Nothing to do with providing a chip to the market for those who want performance 7% slower that the 5370, talk about niche.

If it’s irrelevant when samples appear then we should disregard everything we’ve seen so far about zen, including what you said about there currently only being quad core and octocore and no hexacore samples. Also I didn’t say there were no tricore samples, I said there were no tricore samples “AFAIK”, I wasn’t claiming it to be gospel.

Just saying “quad-core complex is about balance” doesn’t make any point moot because AMD haven’t released anything official to confirm what you’ve said, they’ve not said whether it’s possible or impossible to disabled individual cores but their approach to multicore design has been one of effective cost recuperation for the last 10 years and it’s in their financial interests to continue making chips that are flexible enough to be downgraded, especially as they’ve been hemorrhaging money. In regards to your comment about modern architectures like haswell not being able to disable cores, here’s a quote from PCperspective “All eight cores in the silicon will have access to the cache for the top of the line Core i7-5960X. For the six core models, the i7-5930K and the i7-5820K, one pair of cores is disabled”. So even a modern architecture like haswell can have cores disabled and the same seems to be apparent for the 10 core i7-6950X, 8 core i7-6900K and 6 core i7-6850K.

Also of course you’re going to say my arguments are invalid, that’s just the standard “I’m right, you’re wrong” attitude on the internet. If they don’t have any 6 core products within the first few months of retail release then I’ll be wrong, but I’ll be wrong because of a bad decision on AMDs part, not flawed logic and common sense. AMD need to fill the large price and performance gap and unless the 14nm node does miracles then they’re not going to do it by offering quad cores with stock speeds of 5-6ghz and they’ll lose that segment of the market to Intel with products already available.

TDP is irrelevant to the point I am making. You said that tri-core was not released because the power reduction was small, but I have demonstrated that AMD is releasing variations of Jaguar chips with power deltas are smaller than the one you said was not worth. The real reason why they are not selling tri-core Jaguar was given before.

What I have said is that it is irrelevant when engineering samples appear in public. My claim wasn’t that six-core engineering samples are still hidden to public. My claim is that no six-core engineering sample exists.

AMD has released official information about Zen at HotChips, including a diagram of the core-complex that proves my point. However, I already knew this info before when I found a slide with a die shot of the Zeppelin die. The diagram illustrated the core-complex topology, as Desdrenboy, Hans, and others including myself demonstrated then. AMD only confirmed us at HotChips.

You pretend now that your claim about a six-core Zen CPU relies on “logic and common sense”. But I am saying you that your claim ignores the microarchitecture details, the existing engineering samples, and the official roadmaps given to OEMs.

I want to respond, but I don’t have the motivation to reiterate and clarify points already made only to have them cherry picked again.

Yup my first upgrade since 2008

It will be my second since 2009. 🙂

I’d say the 6 core model is 95% confirmed, gg:

https://www.reddit.com/r/Amd/comments/5n65aj/ryzen_8c16t_f4_3640_engineering_sample_over_95w/

Indeed, thanks!

What were you saying about no 6 cores and not being cheap? R5 1600 for $230

I cannot be always right 😉

? Glad you were wrong on price this time

You can. You’re always right.

Just that the definition of ‘right is reversed!

It looks as your ban at SA got you very very hungry.

Hello. May I ask for your username on S|A?

Hahaha. I have never been banned from ANY website in the world EVER.

Even for calling you a two pence Môthêrfûckîng schîII ! ?

(seems like Disqus agrees with me!)

As far you are considered lets see the list of websites that banned you WHILE HANDING INSULTS that would drown any self-respecting man…

1. RealworldTech. And oh, do I not know remember the slapping piece of mind that David Kanter gave you….which went on to become signature (yes signature!) of many people. ?

I consider Realworldtech forums to be the spiritual successor to Comp arch. discussion board and probably the no. 1 go to place for tech discussion.

2. Semiaccurate. Ohh the ridicule that you get there ???. In your lingo Your SHAMELESSNESS would beat a 32 core 64 thread Xeon-EX clocked @ 4ghz!!

3. Anandtech. While the no. of circle jêrkěrs like you isn’t lacking at that site but still…it’s a good content site, especially many of the detailed/deep-dive articles.

4. HardOCP. Oh no, not HardOCP! That place loves you, Kylê Kôrrůpt Bênnêt must feel blessed to have you divine (fęacal ?) presence there!

5. Many other average or mediocre websites whose forums I don’t go through. PcPer, Tech Report etc don’t exactly have useful forums or at the very least forums I would find any new information at.

A perennial lurker/reader there, man.

Realworldtech is the only tech website where I care to actually WRITE.

Ah okay, like myself. Mainly because I can’t f**king register.

Then you confirm it was a permaban? I believed you were given forced vacations only for the next three months. Too bad you didn’t learn anything…

You proved what you are….an unbelievably stupìd real life dûffer!

I haven’t ever posted on Semiaccurate! There you go ?